#### Layout for Analog Integrated Circuits

- Layout is the process of specifying the physical placement of and interconnections between all of the devices in a circuit.

- Layout is used to generate all of the mask layers used for chip fabrication.

- Layout for digital circuits:

- Usually many transistors

- Many transistors are minimum size

- Transistors are sized to minimize delays

- Focus on interconnections between modules

- Layout for analog circuits:

- Usually relatively few transistors

- Few transistors are minimum size

- Transistors are sized to minimize offsets

- Focus on optimizing individual devices

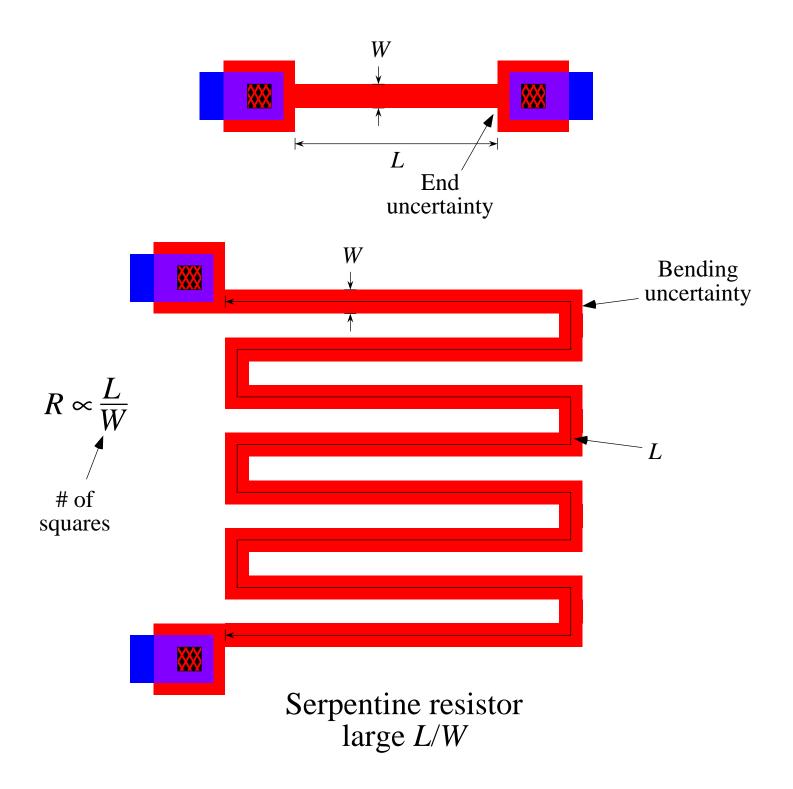

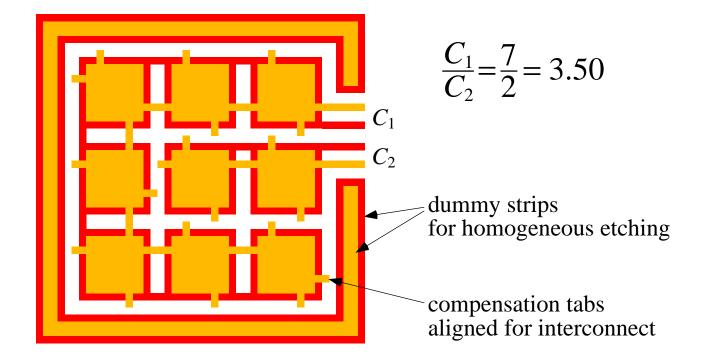

#### Resistors

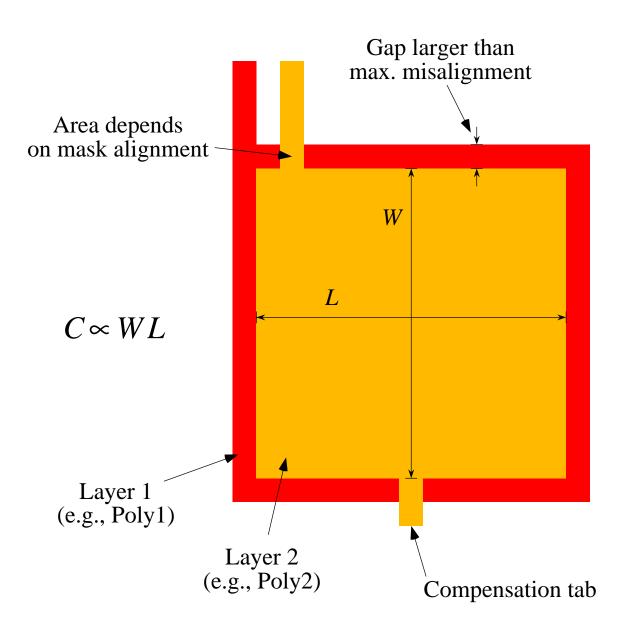

#### Capacitors

### Control of Absolute Component Values

- Control device geometries by avoiding uncertainties. Examples:

- Stacked vs serpentine MOS transistors

- Bending uncertainties in a resistor controlled by a low resistivity layer

Avoid using minimum dimensions.

$$R = R_{\Box} \frac{L}{W} \qquad C = C_{S}WL$$

$$\frac{\Delta R}{R} = \frac{\Delta R_{\Box}}{R_{\Box}} + \frac{\Delta L}{L} - \frac{\Delta W}{W} \qquad \frac{\Delta C}{C} = \frac{\Delta C_{S}}{C_{S}} + \frac{\Delta L}{L} + \frac{\Delta W}{W}$$

indep. of minimize by making  $W >> W_{min}$

$\sim 5 - 50\%$  and  $L >> L_{min}$

$$C = C_{S}WL$$

indep. of minimize by minimize by minimize by making  $W >> W_{min}$

$\sim 5 - 50\%$  and  $L >> L_{min}$

Good circuit designs minimize reliance on absolute component values.

#### Layout for Device Matching

Devices on the same die can match well (precision):

$$\frac{\Delta C}{C} \sim 0.1\% \qquad \frac{\Delta R}{R} \sim 0.1\% \qquad \frac{\Delta I_{\rm s}}{I_{\rm s}} \sim 1-10\%$$

For circuits characteristics (e.g., gains) that depend on ratios of component values,

Precise matching  $\Rightarrow$  Accurate characteristics

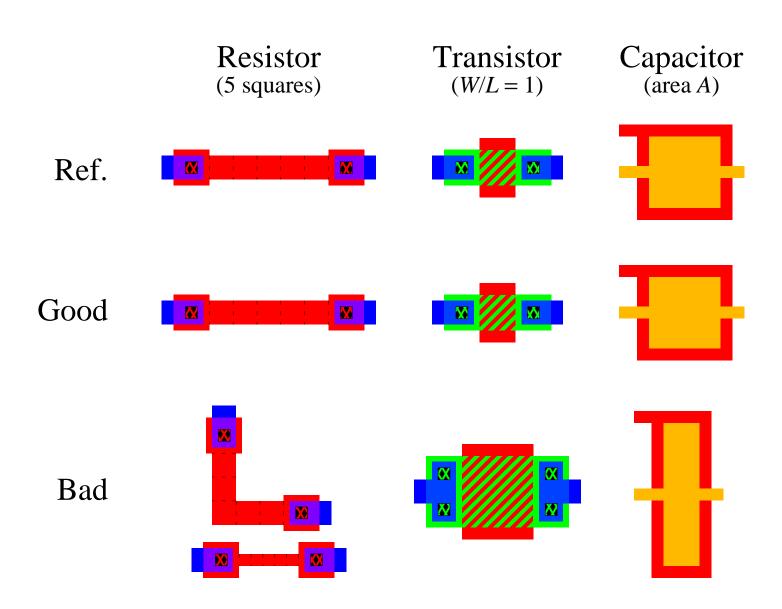

To improve device matching, use devices with

- Same temperature

- Identical shape and size

- Minimum spacing

- Common centroid geometries

- Same orientation

- Same surroundings

- Nonminimum size

Caveat emptor! The relevance of each "rule" depends on particulars of the process and devices involved.

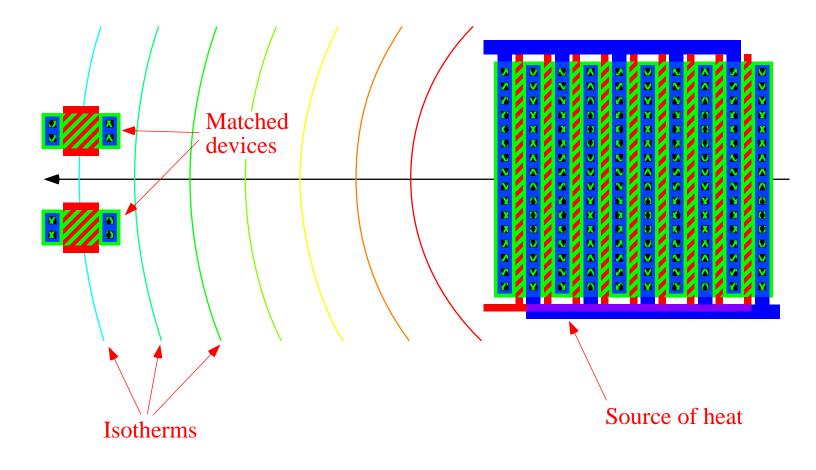

### Matching: Same Temperature

- Not a serious problem if the total power dissipation on chip is low enough (e.g., subthreshold CMOS).

- Place devices symmetrically with respect to the source of heat along an isotherm:

## Matching: Identical Shape and Size

## Matching: Minimum Distance

- Take advantage of spatial correlations.

- Place devices as close together as possible.

- Examples:

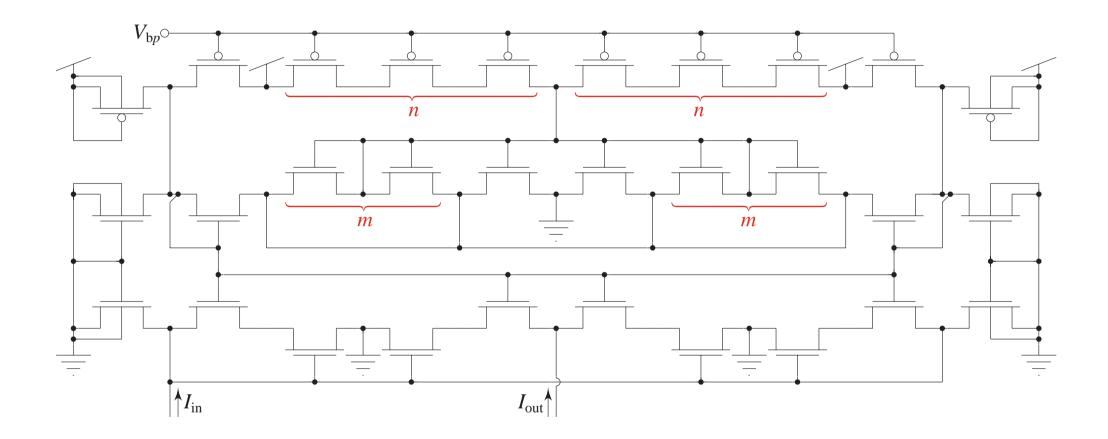

3-Output Current Mirror

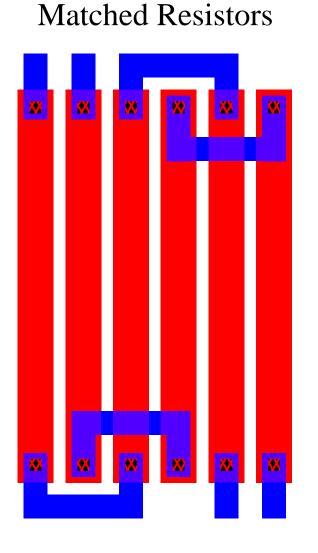

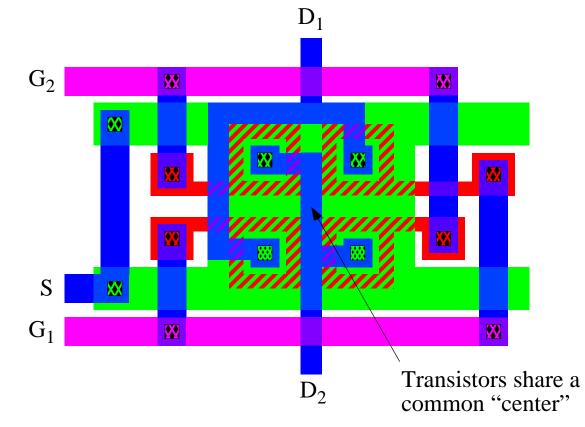

## Matching: Common Centroid

Compensation of constant gradients

- Temperature

- Oxide thickness

- Substrate Doping

- Example: Cross-coupled quad

► Complicated layout  $\Rightarrow$  not practical for > 2×2

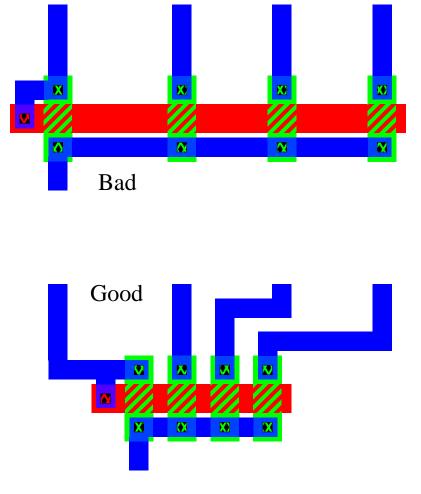

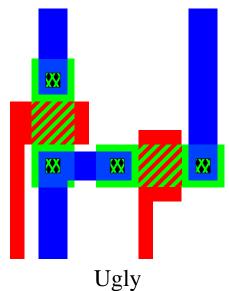

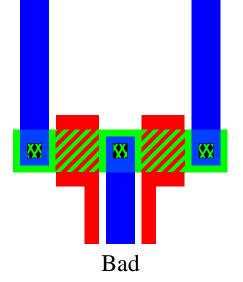

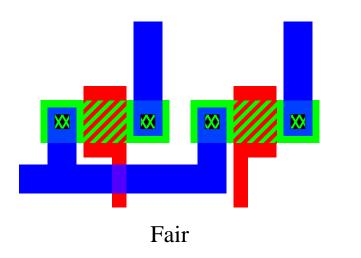

### Matching: Same Orientation

Eliminate mismatch arising from:

- Anisotropic substrate

- Anisotropic process steps

- Packaging-induced stresses

Example: Differential Pair

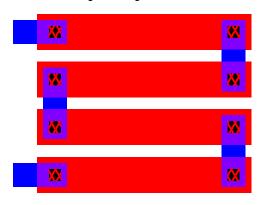

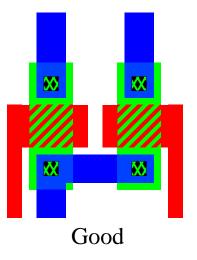

# Matching: Same Surroundings

Reasons are not always clear. Possibilities include:

- Fringing fields

- Nonuniform lithography

- Nonuniform etching during processing

- Use dummy devices to make all functional devices have the same surroundings.

- Examples:

Sometimes the surround can be simulated adequately with dummy strips.

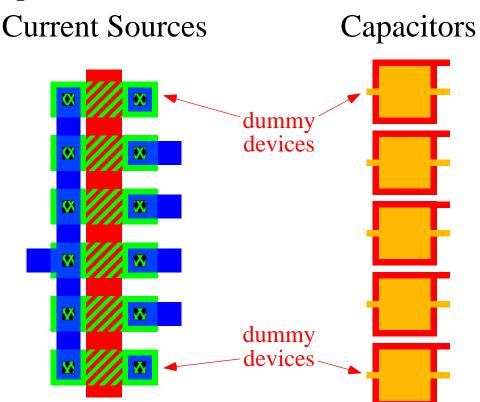

### Matching for Non-Unity Ratios

For n/m ratios, use n+m unit devices:

**Example:** Capacitors

#### Matching for Non-Unity Ratios

For arbitrary ratios, violate matching rules optimally. Examples:

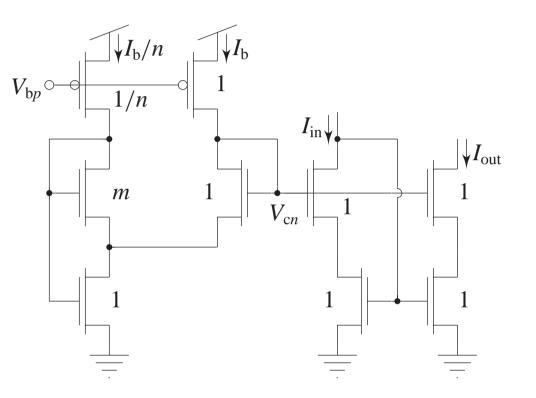

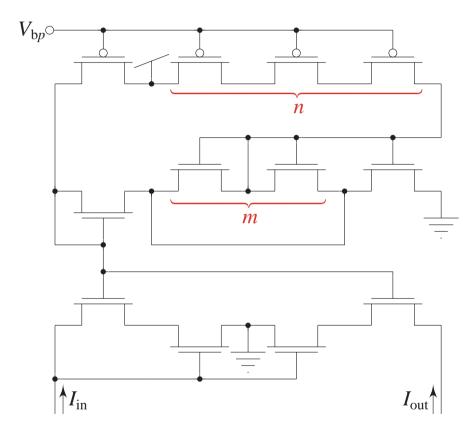

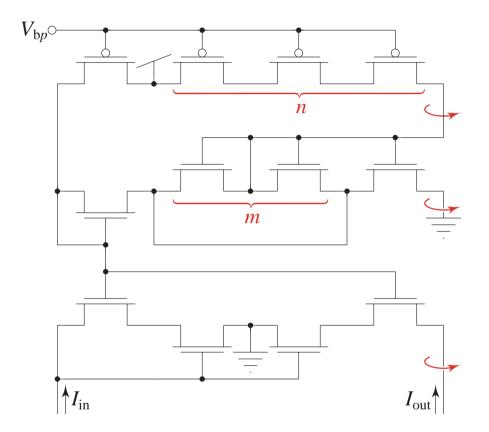

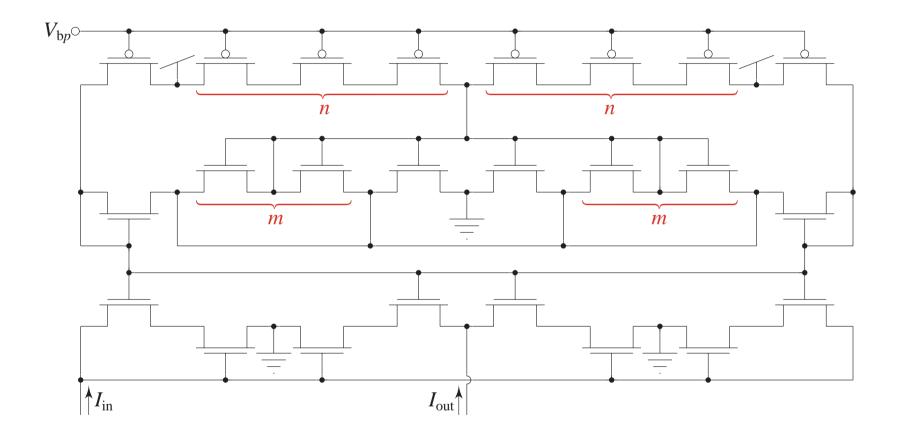

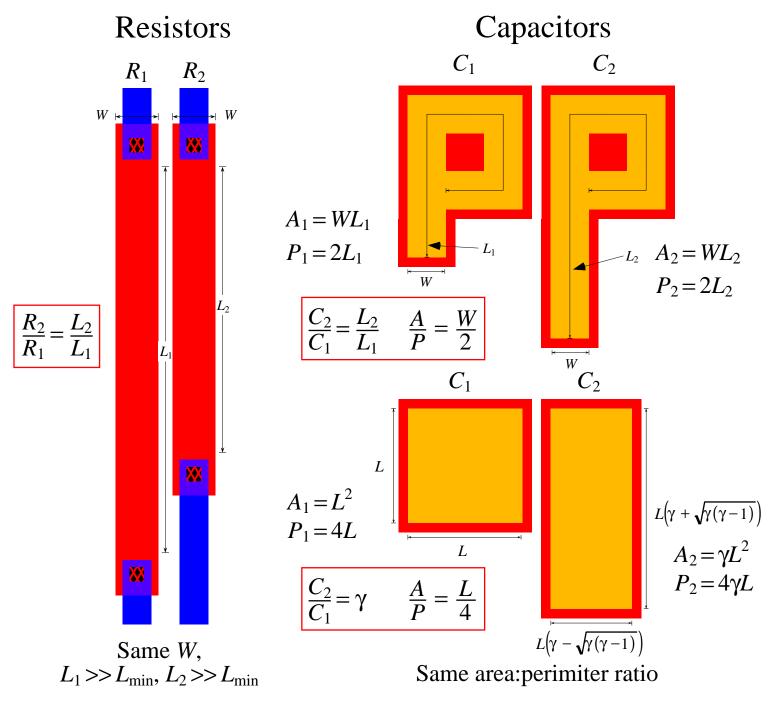

#### Layout Considerations for a Low-Voltage Cascode Current Mirror

- To get accurate ratios, we implement the *n*MOS of width *m* as a parallel connection of *m* unit transistors.

- Similarly, we implement the *p*MOS of length *n* as a series connection of *n* unit transistors.

- If we choose *m* to be even, we can optimally share source/drain regions of the *n*MOS transistors in the bias circuit.

- If we choose n = m + 1, we have as many *p*MOS strips as *n*MOS strips.

ORNELI