# United States Patent [19]

#### Minch et al.

# [11] **Patent Number:** 5,986,927

## [45] **Date of Patent:** Nov. 16, 1999

#### [54] AUTOZEROING FLOATING-GATE AMPLIFIER

#### [75] Inventors: Bradley A. Minch; Paul E. Hasler,

both of Pasadena; Christopher J. Diorio, Torrance; Carver A. Mead,

Pasadena, all of Calif.

[73] Assignee: California Institute of Technology,

Pasadena, Calif.

[21] Appl. No.: 09/189,595

[22] Filed: Nov. 10, 1998

#### Related U.S. Application Data

[62] Division of application No. 08/721,261, Sep. 26, 1996, Pat. No. 5,875,126.

[60] Provisional application No. 60/004,566, Sep. 29, 1995.

[51] Int. Cl.<sup>6</sup> ...... G11C 16/04

#### [56] References Cited

#### U.S. PATENT DOCUMENTS

| 3,893,151 | 7/1975  | Bosselaar et al 357/23  |

|-----------|---------|-------------------------|

| 4,420,871 | 12/1983 | Scheibe                 |

| 4,622,656 | 11/1986 | Kamiya et al 365/185    |

| 4,822,750 | 4/1989  | Perlegos et al 437/52   |

| 4,935,702 | 6/1990  | Mead et al 330/9        |

| 4,953,928 | 9/1990  | Anderson et al 357/23.5 |

| 5,059,920 | 10/1991 | Anderson et al 330/253  |

| 5,068,622 | 11/1991 | Mead et al              |

| 5,146,106 | 9/1992  | Anderson et al 307/246  |

| 5,160,899 | 11/1992 | Anderson et al 330/288  |

| 5,166,562 | 11/1992 | Allen et al 307/571     |

| 5,331,215 | 7/1994  | Allen et al 307/201     |

| 5,336,936 | 8/1994  | Allen et al 307/201     |

| 5,345,418 | 9/1994  | Challa 365/185          |

|           |         |                         |

(List continued on next page.)

#### OTHER PUBLICATIONS

Diorio, et al., "A High–Resolution Non-Volatile Analog Memory Cell," 1995, IEEE Intl. Symp. on Circuits and Systems, vol. 3, pp. 2233–2236.

Gray, et al., "Analysis and Design of Analog Integrated Circuits", 1984, John Wiley & Sons, pp. 67–71.

Hasler, et al., "An Autozeroing Amplifier Using PFET Hot-Electron Injection", May 12-15 1996, IEEE International Symposium on Circuits and Systems, vol. 3.

Hasler, et al., "Single Transistor Learning Synapse", 1995, Advances in Neural Information Processing Systems 7, MIT Press, pp. 817–824.

Hasler, et al., "Single Transistor Learning Synapse with Long Term Storage," 1995, IEEE Intl. Symp. on Circuits and Systems, vol. 3, pp. 1660–1663.

(List continued on next page.)

Primary Examiner—Huan Hoang Attorney, Agent, or Firm—D'Alessandro & Ritchie

#### [57] ABSTRACT

An autozeroing floating-gate amplifier (AFGA) is an integrated continuous-time filter that is intrinsically autozeroing. It can achieve a highpass characteristic at frequencies well below 1 Hz. In contrast with conventional autozeroing amplifiers that eliminate their input offset, the AFGA nulls its output offset. The AFGA is a continuous-time filter; it does not require any clocking. The AFGA includes at least one floating-gate MOS transistor that is capable of hotelectron injection of electrons onto the floating gate of the MOS transistor. Electrons are continuously removed from the floating gate(s), for example, via Fowler-Nordheim tunneling. The AFGA has a stable equilibrium for which this tunneling current is balanced by an injection current of equal magnitude. When the circuit is driven away from its equilibrium by an input or something else, an imbalance between the tunneling and injection current charges (if the tunneling current exceeds the injection current) or discharges (if the injection current exceeds the tunneling current) the floating gate(s) until the equilibrium is re-established. The equilibrium is chosen to achieve a desired baseline of operation.

#### 6 Claims, 20 Drawing Sheets

#### U.S. PATENT DOCUMENTS

| 5,463,348 | 10/1995 | Sarpeshkar et al 330/253    |

|-----------|---------|-----------------------------|

| 5,541,878 | 7/1996  | LeMoncheck et al 365/185.03 |

| 5,627,392 | 5/1997  | Diorio et al                |

| 5,687,118 | 11/1997 | Chang 365/185.19            |

| 5,734,288 | 3/1998  | Dolazza et al 327/337       |

| 5,763,912 | 6/1998  | Parat et al 257/315         |

| 5,773,997 | 6/1998  | Stiegler 327/53             |

| 5,777,361 | 7/1998  | Parris et al                |

#### OTHER PUBLICATIONS

Hochet, et al., "Implementation of a Learning Kohonen Neuron Based on a New Multilevel Storage Technique", Mar. 1991, IEEE J. Solid–State Circuits, vol. 26, No. 3, pp. 262–267.

Hollis, et al., "A Neural Network Learning Algorithm Tailored for VLSI Implementation", Sep. 1994, IEEE Trans. on Neural Networks, vol. 5, No. 5, pp. 784–791.

Hu, et al., "Hot-Electron-Induced MOSFET Degradation—Model, Monitor, and Improvement", Feb. 1985, IEEE Transactions on Electron Devices, vol. ED-32, No. 2, pp. 375–385.

Ismail, "Neural Information Processing II," 1994, Analog VLSI Signal and Information Process, New York: McGraw-Hill, Inc., pp. 358–413.

Johnson, "Neural Team Bares Silicon Brain", Jul. 3, 1995, Electronic Engineering Times, p. 1 and 31.

Johnson, "Mead Envisions New Design Era", Jul. 17, 1995, Electronic Engineering Times, pp. 1, 37, 38.

Lazarro et al., "Winner-Take-All Networks of O(N) Complexity," 1989, in D. S. Touretzky, ed., Advances in Neural Information Processing Systems 1, San Mateo, CA; Morgan Kaufmann, pp. 703–711.

Lazzaro, et al., "Systems Technologies for Silicon Auditory Models," Jun. 1994, IEEE Micro, vol. 14, No. 3, pp. 7–15, T

Leblebici, et al., "Hot-Carrier Reliability of MOS VLSI Circuits", 1993, Kluwer Academic, 46-49.

Masuoka, et al., "Reviews and Prospects of Non–Volatile Semiconductor Memories," Apr. 1991, IEICE Trans., vol. E 74, No. 4, pp. 868–874.

Mead, et al., Introduction to VLSI Systems, Addison-Wesley Pub. Co., 1980, pp. 1–5.

Minch, "A vMOS Soft-Maximum Current Mirror," 1995 IEEE, vol. 3, pp. 2249–2252.

Minch, et al., "Translinear Circuits Using Subthreshold Floating-Gate MOS Transistors," 1996, Analog Integrated Circuits and Signal Processing, vol. 9, No. 2 pp. 167–179. Sanchez, et al., "Review of Carrier Injection in the Silicon/Silicon-Dioxide System", Jun. 1991, IEEE Proceedings-G, vol. 138, No. 3, pp. 377–389.

Sarpeshkar, et al., "White Noise in MOS Transistors and Resistors," Nov. 1993, IEEE Circuits and Devices, pp. 23–29.

Tsividis, et al., "Continuous-Time MOSFET-C Filters in VLSI", Feb. 1986, IEEE Transactions on Circuits and Systems, vol. 33, No. 2, pp. 125–140.

FIG. 1

FIG. 2

FIG. 3

FIG. 4A

FIG. 4B

FIG. 5A

FIG. 5B

FIG. 6A

FIG. 6B

FIG. 7A

FIG. 7B

FIG. 8A

FIG. 8B

FIG. 9A

FIG. 9B

FIG. 10A

FIG. 10B

FIG. 11B

FIG. 11C

Nov. 16, 1999

FIG. 12

FIG. 13A

FIG. 13B

FIG. 14

FIG. 15

FIG. 16

FIG. 17B

FIG. 18A

FIG. 18B

FIG. 19A

FIG. 19B

$V_{in}$  $\stackrel{C_1}{\smile}$ H

-||-C₁

V<sub>τ1 o</sub>--

$V_{\text{tun}}$   $V_{\text{dd}}$   $V_{$

158

V<sub>τ3</sub> o-

160

FIG. 21

156

$V_{\tau 2} \circ \longrightarrow$

FIG. 22  $V_{tun}$  $V_{tun}$  $V_{tun} \\$  $V_{dd}$  $C_1$  $C_1$  $C_1$ C<sub>2</sub>=  $C_2 \stackrel{\downarrow}{=}$  $C_2$ -∘V<sub>out2</sub> ⊸V<sub>out1</sub>  $I_{out2}$ I<sub>outN</sub>  $\circ V_{\mathsf{outN}}$ I<sub>out1</sub>  $I_{in2}$ *I*<sub>inN</sub>  $I_{in1}$

FIG. 23

FIG. 24A

FIG. 24B

#### AUTOZEROING FLOATING-GATE **AMPLIFIER**

#### CROSS-REFERENCE TO RELATED APPLICATIONS

This application claims the benefit of United States Provisional Patent Application Serial No. 60/004,566 filed Sep. 29, 1995 in the names of the inventors hereof and commonly assigned herewith and is a division of U.S. patent application Ser. No. 08/721,261, filed Sep. 26, 1996 now U.S. Pat. No. 5,895,126, in the names of the inventors hereof and commonly assigned herewith.

#### STATEMENT AS TO RIGHTS TO THE INVENTION

The present invention was made with support from the United States Government under Grant number N0001489-J-1675 awarded by the Office of Naval Research of the Department of the Navy and under Grant number N00014- 20 89-J-3083 awarded by the Advanced Research Projects Agency of the Department of Defense. The United States Government has certain rights in the invention.

#### BACKGROUND OF THE INVENTION

#### 1. Field of the Invention

The present invention is directed to a bandpass floatinggate amplifier that uses tunneling and pFET hot-electron injection so that the amplifier returns to its sensitive region 30 despite large changes in the DC input voltage.

### 2. The Prior Art

Offsets often present a difficult problem for designers of MOS analog circuits. A time-honored tradition for addressing this problem is to use a blocking capacitor to eliminate 35 the input DC component; however, for integrated filters, this approach requires enormous input capacitors and resistors to get time-constants of less than 1 Hz. Existing on-chip autozeroing techniques rely on clocking schemes that compute the input offset periodically and then subtract the 40 correction from the input. See, e.g., E. A. Vittoz, "Dynamic analog techniques", in Y. Tsividis and P. Antognetti, Design of MOS VLSI Circuits for Telecommunications, Prentice Hall, 1985. These autozeroing techniques add significant complexity to the circuit, as well as clock noise, aliasing, 45 and other problems. Accordingly, there is a need for improved autozeroing techniques and apparatus.

Prior floating-gate transistor devices, which utilize electrical charge stored in a floating polysilicon gate imbedded in an insulator such as silicon dioxide, provide a method of 50 storing analog values as a quantity of electrical charge on an integrated circuit chip. The charge on such a floating gate is known to remain fixed for periods of up to many years. Although the advantages of using floating gate transistors as tems Technologies for Silicon Auditory Models," IEEE Micro, Vol. 14, No. 3, 1994, pp. 7-15, T. Allen, et al., U.S. Pat. No. 5,166,562, entitled: "Writable Analog Reference Voltage Storage Device," they have not been used previously to construct bandpass amplifiers. The principal reason has been the lack of a suitable bi-directional mechanism for writing and erasing the offset. Since the gate of a floating gate transistor is completely embedded within an insulator, writing the memory involves moving charge carriers through this insulator. Two non-light-based mechanisms are 65 known which will move electrons through an insulator. These are tunneling and hot-electron injection. The inherent

difficulty in performing these operations has been a primary impediment to the implementation of floating gate transistors in such systems.

Transporting electrons across the barrier presented by the silicon/oxide interface requires that an electron possess more than about 3.1 eV of energy. At room temperature the probability that semiconductor electrons will possess this amount of energy is exceedingly small. Alternatively, an electron could tunnel through this barrier; however, at the voltages and oxide thicknesses used in conventional silicon MOS processing, the tunneling probability is also exceedingly small.

Fowler-Nordheim tunneling involves applying a voltage across the oxide which enhances the probability of an electron tunneling through it. Bi-directional oxide currents are required to achieve a balance of current into or out of a bandpass amplifier. Although the tunneling process has no preferred direction, bi-directional tuneling requires either dual polarity high voltages, or a single polarity high voltage and a means for pulling the floating gate to this voltage when adding electrons, and pulling it near ground when removing them. Both approaches are unattractive. The dual polarity solution requires a negative voltage much lower than the substrate potential; the single polarity solution does not support simultaneous "reading" and "writing".

Single polarity bi-directional tunneling is often used in writing digital EEPROMs. Since writing the memory involves pulling the floating gate either to the supply voltage or to ground, the EEPROM cell cannot be read during the write process. Excess charge is typically added to the floating gate to compensate for this lack of memory state feedback. Although excess charge is acceptable when writing a binary valued "digital" memory, where the exact quantity of charge is irrelevant once it exceeds the amount necessary to completely switch the device to one of its two binary states, uncertainty in the amount of charge applied to an analog device is unacceptable for bandpass amplifier applications.

Hot-electron injection is a process whereby electrons near the surface of a semiconductor acquire more than about 3.1 eV of energy, typically by acceleration in an electric field, and then surmount the silicon/silicon-dioxide barrier. Once in the silicon dioxide conduction band, an electric field applied across the oxide carries these electrons to the floating gate. There are a number of ways of accomplishing hot-electron injection.

One source for a high electric field is a depletion region. For instance, the collector-to-base depletion region of either a vertical or lateral BJT (bipolar junction transistor) can be used. An example of a lateral BJT used in a similar application is shown in U.S. Pat. No. 4,953,928 to Anderson, et al. Alternatively, the channel-to-drain depletion region of a high-threshold N-type MOSFET in a moderately doped memory elements are well known, J. Lazzaro, et al., "Sys- 55 substrate can be used. An example of such a device used in a similar application is shown in U.S. patent application, Ser. No. 08/399,966 filed on Mar. 7, 1995 by Diorio, et al. Finally, the drain-to-channel depletion region of a subthreshold P-type MOSFET can be used. Hot-electron injection in such devices is usually thought of as a source of oxide degradation in MOSFETs, Y. Leblebici and S. M. Kang, Hot Carrier Reliability of MOS VLSI Circuits, Kluwer Academic, 1993. Nonetheless, this process can be reliably and safely used as a mechanism to adapt the charge stored on a floating-gate MOSFET as shown herein.

> Another source for a high electric field is the channel region of a split-gate N-type MOSFET. Split-gate injectors,

as shown and described in U.S. Pat. No. 4,622,656 to Kamiya, et al., contain two partially overlapping gate regions at very different voltages. The resulting surface potential drops abruptly at the interface between the two gates, creating a high electric field localized in this small 5 region of the transistor channel.

#### SUMMARY OF THE INVENTION

The present invention is directed to a novel device known as an autozeroing floating-gate amplifier (AFGA). The AFGA is an integrated continuous-time filter that is intrinsically autozeroing. It can achieve a highpass characteristic at frequencies well below 1 Hz. In contrast with conventional autozeroing amplifiers that eliminate their input offset, the AFGA nulls its output offset. The AFGA is a continuoustime filter; it does not require any clocking. According to the invention, an AFGA includes at least one floating-gate MOS transistor that is capable of hot-electron injection of electrons onto the floating gate of the MOS transistor. Electrons are continuously removed from the floating gate(s), for example, via Fowler-Nordheim tunneling. The AFGA has a stable equilibrium for which this tunneling current is balanced by an injection current of equal magnitude. When the circuit is driven away from its equilibrium by an input or something else, an imbalance between the tunneling and 25 injection current charges (if the tunneling current exceeds the injection current) or discharges (if the injection current exceeds the tunneling current) the floating gate(s) until the equilibrium is re-established. The equilibrium is chosen to achieve a desired baseline of operation.

#### OBJECTS AND ADVANTAGES OF THE **INVENTION**

An object and advantage of the present invention is to provide an autozeroing floating-gate amplifier.

Another object and advantage of the present invention is to provide a band pass floating-gate amplifier implemented in an analog MOS circuit and capable of automatically returning to its sensitive regime despite large changes in its 40 DC inputs.

Another object and advantage of the present invention is to provide improved autozeroing photoreceptor circuits.

Another object and advantage of the present invention is to provide improved autozeroing sensor input circuits.

Another object and advantage of the present invention is to provide an autozeroing differentiator circuit.

Another object and advantage of the present invention is to provide a tunable, autozeroing second-order filter which can be cascaded to form silicon cochleas.

Another object and advantage of the present invention is to provide improved winner-take-all (WTA) circuits.

Another object and advantage of the present invention is to provide autozeroing floating-gate MOS translinear cir-  $_{55}$ cuits.

Yet another object and advantage of the present invention is to provide an autozeroing, first-order log-domain filter.

These and many other objects and advantages of the present invention will become apparent to those of ordinary skill in the art from a consideration of the drawings and ensuing description of the invention.

#### BRIEF DESCRIPTION OF THE DRAWINGS

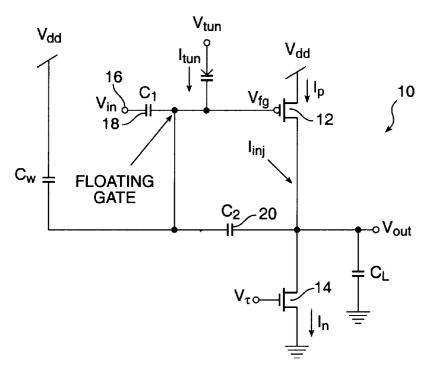

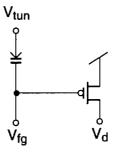

FIG. 1 is an electrical schematic diagram of an autozero- 65 ( $V_{tun}$ ). ing floating-gate amplifier (AFGA) that uses pFET hotelectron injection.

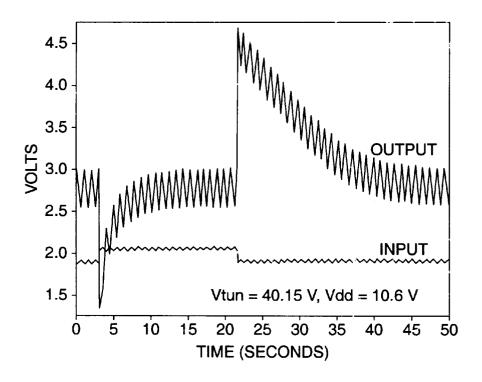

- FIG. 2 is a voltage vs. time response of the AFGA to a 1 Hz sinewave superimposed on a 19 s voltage pulse. The AFGA has a closed-loop gain of 11.2, and a low-frequency cutoff at 100 mHz.

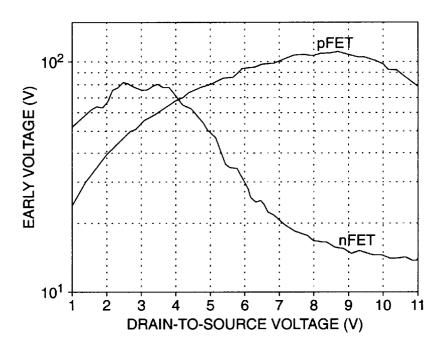

- FIG. 3 shows the effect of drain-to-source voltage on the Early voltage of an nFET and pFET.

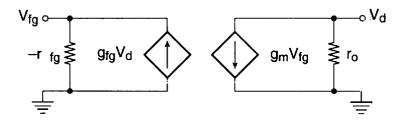

- FIGS. 4A and 4B depict a small-signal model of a pFET with the effects of hot-electron injection.

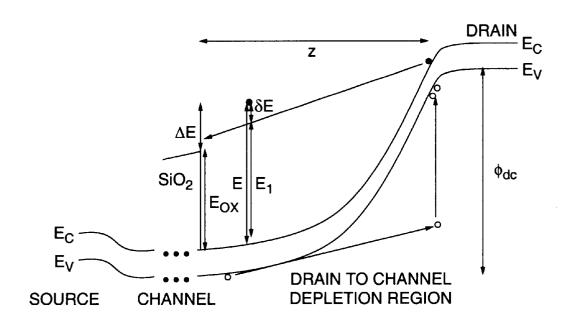

- FIG. 5A is a band diagram of a subthreshold pFET transistor under conditions favorable for hot-electron injec-

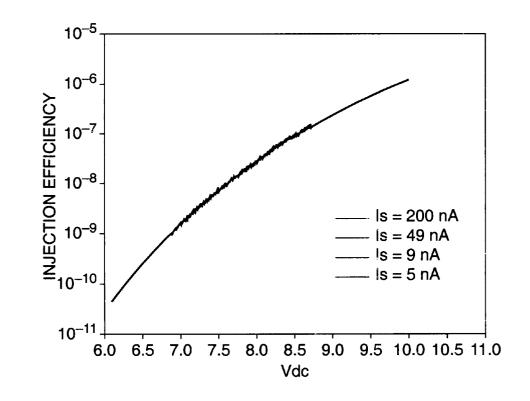

- FIG. 5B is measured data of pFET injection efficiency verses the drain-to-channel voltage for four source currents.

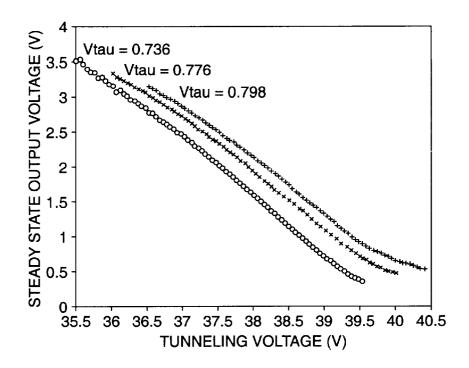

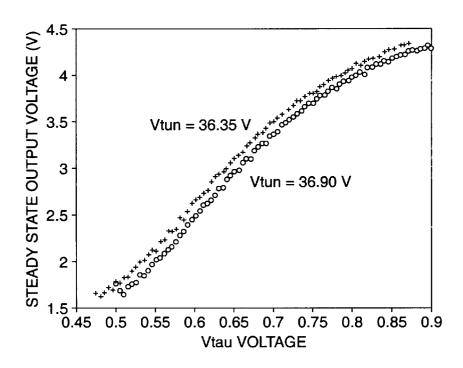

- FIG. 6A shows the steady-state output voltage versus the tunneling voltage in an AFGA for three values of V<sub>r</sub>.

- FIG. 6B shows the steady-state output voltage versus V, in an AFGA for two tunneling voltages.

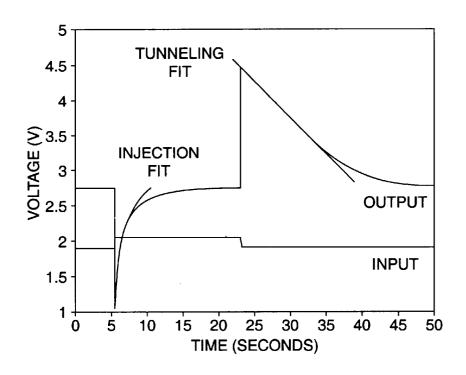

- FIGS. 7A-7B shows the response of an AFGA to an upgoing and downgoing step input. The adaptation in response to an upward step results from electron tunneling; the adaptation in response to a downward step results from pFET hot-electron injection.

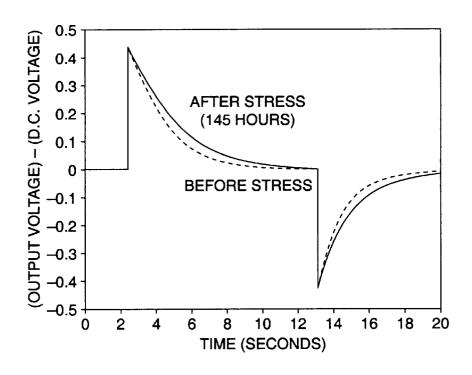

- FIG. 8A shows the response of an AFGA to an upgoing and downgoing voltage step before and after 145 hours of

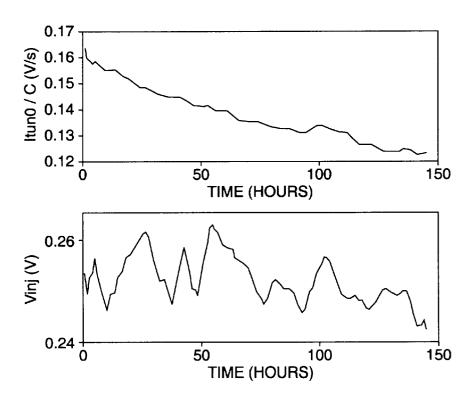

- FIG. 8B shows the extracted device parameters of the AFGA as a function of time.

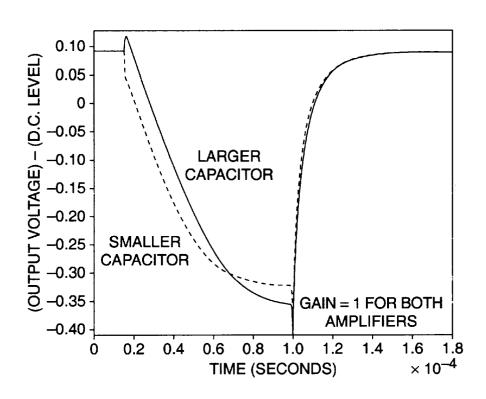

- FIG. 9A shows voltage vs. time curves for two AFGAs with unity gain as shown, but with each having different values for  $C_1$ .

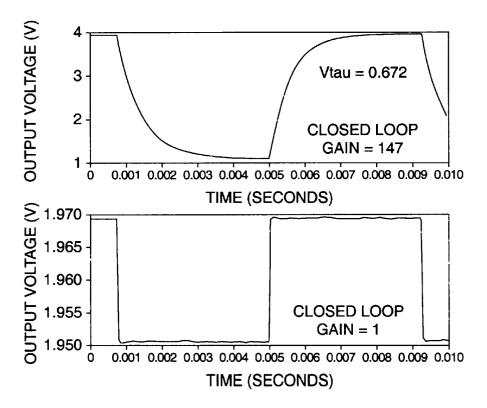

- FIG. 9B shows voltage vs. time curves for two AFGAs with different gains.

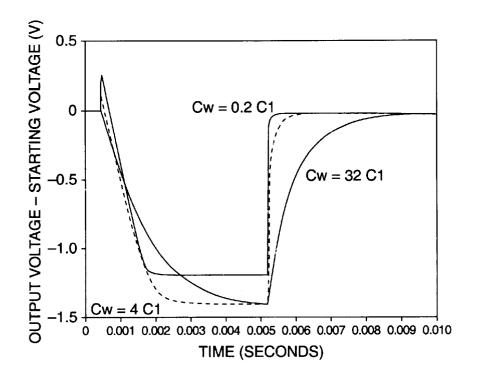

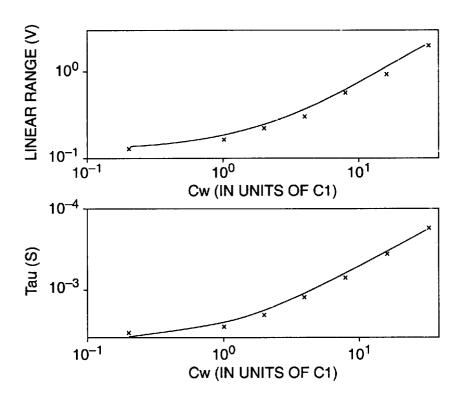

- FIG. 10A shows the response of three AFGAs to the same square wave input. Here all three AFGAs were the same except for their values of C<sub>w</sub> and were biased by the same

- FIG. 10B shows the measured linear range and  $\tau_h$  for several unity-gain AFGAs for different C<sub>w</sub> ratioed in units of  $C_1$ . Both curves in FIG. 10B are fitted with a linear equation.

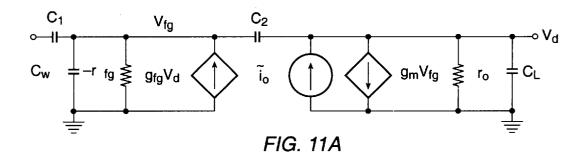

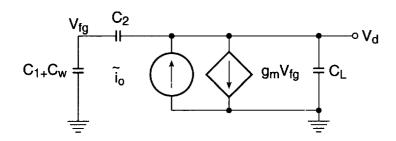

- FIGS. 11A, B and C depict an AFGA represented as a small-signal circuit.

- 45 FIG. 11A shows the small-signal AFGA model using the small-signal pFET model.

- FIG. 11B shows the small-signal model of the effect of the noise source in the channel on the output voltage. The effect of the gate current and the Early voltage effect has been neglected here.

- FIG. 11C shows a simplified small-signal model of the effect of noise.

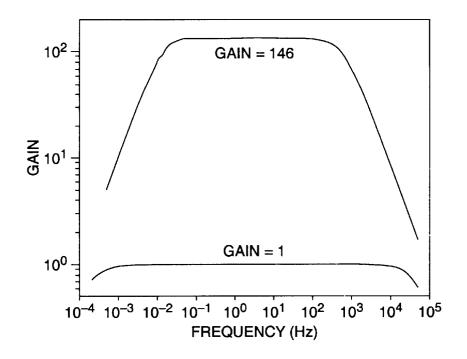

- FIG. 12 shows the frequency response for two AFGAs with different gains. For both the high-and low-gain AFGA,  $C_1+C_2$  is approximately constant. For the high-gain AFGA,  $\tau_1$  is 8 sec, and  $\tau_h$  is 265  $\mu$ sec; for the low-gain AFGA,  $\tau_1$ is 530 sec and  $\tau_h$  is 4  $\mu$ sec. The ratio of  $\tau_h$  and  $\tau_1$  between the two AFGAs are equal to half of the ratio of the gains, which is consistent with a constant  $C_1+C_2$ .

- FIGS. 13A-B depict a noise spectrum of an AFGA for a constant input.

- FIG. 13A shows the output noise spectrum of an AFGA with a gain of 146 for two different tunneling voltages

- FIG. 13B shows a comparison of a high-gain AFGA with a unity gain AFGA and a generic follower-connected dif-

- /- - - /-

ferential amplifier. All three amplifiers had the same  $V_t$  voltage, and correspondingly had the same bias current. The sum of  $C_1$  and  $C_2$  is the same for both AFGAs.

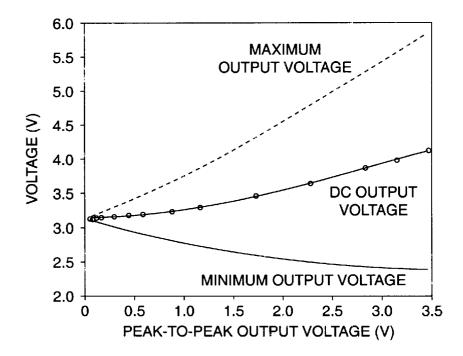

FIG. 14 shows, for an AFGA with a gain of 146, the minimum and maximum output voltages verses peak-to-peak output-voltage amplitude. The frequency of the input sine wave was 100 Hz.

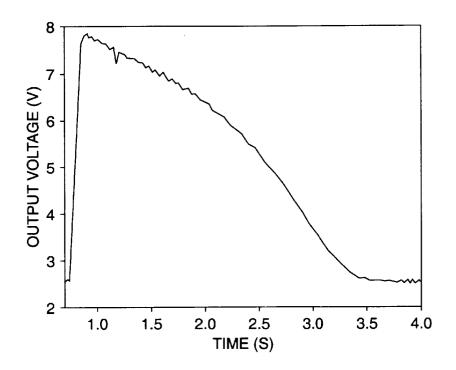

FIG. 15 shows the response of an above threshold autozero amplifier to a slow downgoing step.

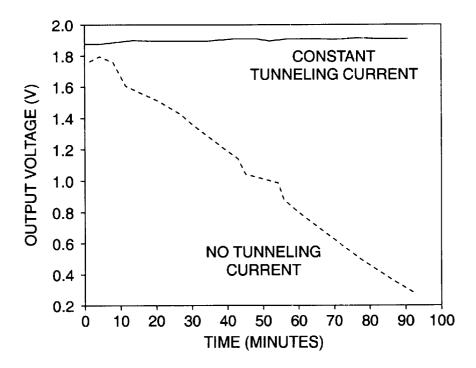

FIG. 16 shows the change in the AFGA output voltage with and without a continuous tunneling current. An AFGA with a gain of 146 was used for each case. The case for no tunneling current also required dropping the power supply;  $V_{dd}$  was set at 5V. The trace with no tunneling current was taken five minutes after the tunneling line was dropped.

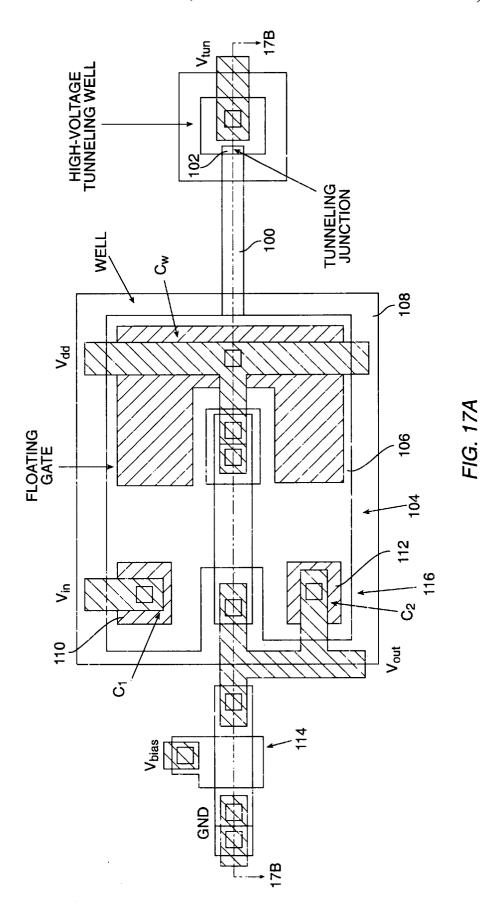

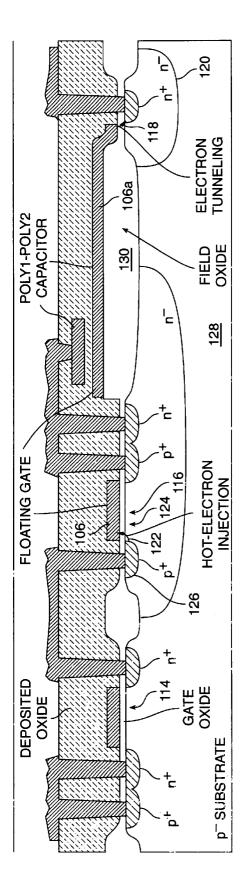

FIGS. 17A-B depict an implementation of an AFGA according to a presently preferred embodiment of the present invention in a 2-micron n-well CMOS process.

FIG. 17A shows a top plan view of an AFGA device.

FIG. 17B shows a vertical cross-sectional view of the AFGA taken along line 17B—17B of FIG. 17A.

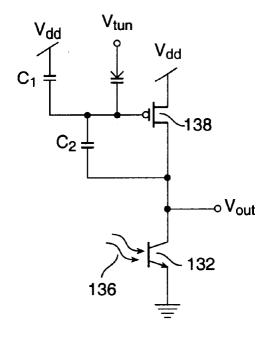

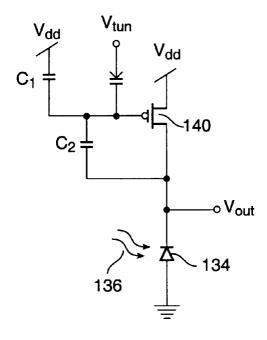

FIGS. 18A-B show circuits for two autozeroing photoreceptors:

FIG. 18A utilizes a phototransistor and

FIG. 18B utilizes a photodiode.

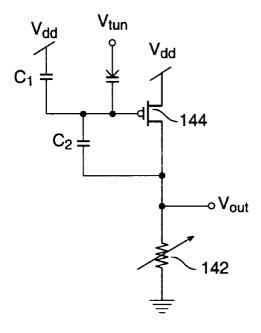

FIGS. 19A-B show the use of an AFGA with certain generic types of sensors.

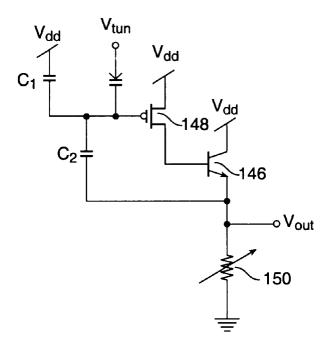

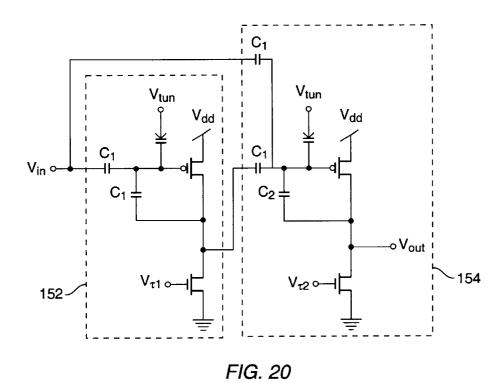

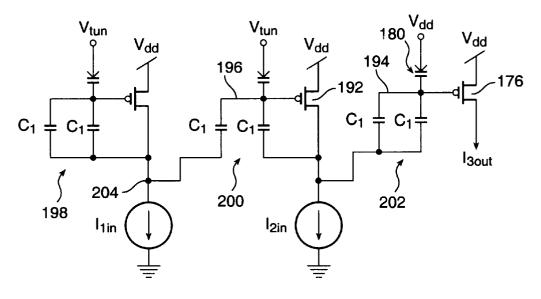

FIG. 20 depicts the circuit of an autozeroing differentiator. 30

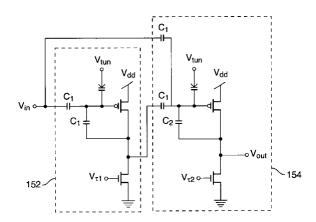

FIG. 21 depicts the circuit of a tunable, autozeroing second-order filter which can be cascaded to form silicon cochleas.

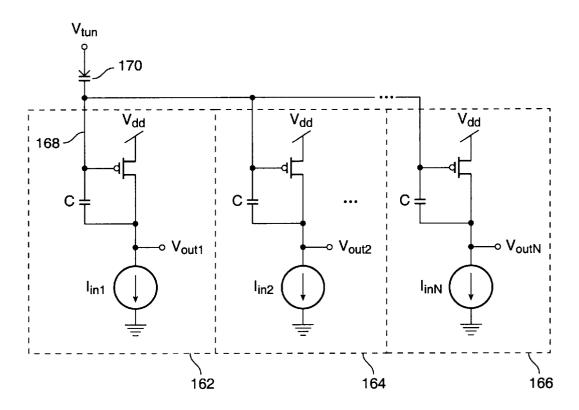

FIG. 22 depicts an autoranging winner-take-all (WTA) circuit.

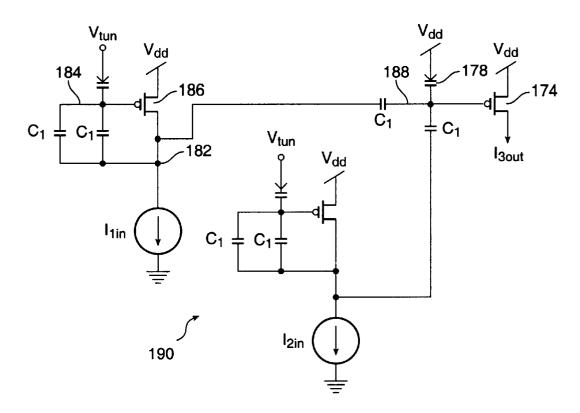

FIG. 23 depicts an autozeroing version of a WTA circuit. FIGS. 24A-B depict autozeroing floating-gate MOS

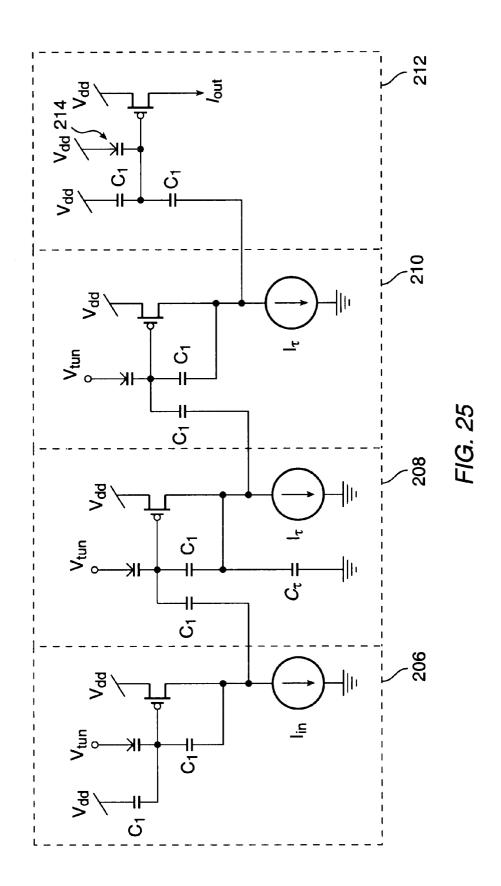

FIG. 25 depicts the circuit for an autozeroing first-order  $_{40}$  log-domain filter.

# DESCRIPTION OF THE PREFERRED EMBODIMENTS

Those of ordinary skill in the art will realize that the 45 following description of the present invention is illustrative only and is not intended to be in any way limiting. Other embodiments of the invention will readily suggest themselves to such skilled persons from an examination of the within disclosure.

Structure of the AFGA

translinear circuits.

FIG. 1 is an electrical schematic diagram of an autozeroing floating-gate amplifier (AFGA) 10 that uses pFET hotelectron injection according to a presently preferred embodiment of the present invention. Until now, pFET hot-electron 55 injection has attracted attention only as a source of MOSFET oxide degradation, Y. Leblebici and S. M. Kang, Hot Carrier Reliability of MOS VLSI Circuits, Kluwer Academic, 1993, therefore this circuit presents an interesting case of "turning a bug into a feature." The capacitance from the floating gate to ground, C<sub>w</sub>, represents both the parasitic and the explicitly drawn capacitances. Increasing Cw will increase the linear input range of the circuit. The capacitance connected to the output terminal,  $C_L$ , is the load capacitance. Between  $V_{tun}$ and  $V_{fg}$  is the symbol used herein for a tunneling junction, which is a capacitor between the floating-gate and an n-well. The open-loop inverting amplifier consists of a pFET input

transistor 12, and an nFET current source 14 which sets the current through pFET 12. With capacitive feedback, the input signal on line 16 is amplified by a closed-loop gain approximately equal to  $-C_1/C_2$  where  $C_1$  is the value of capacitor 18 and  $C_2$  is the value of capacitor 20. The

capacitor 18 and C<sub>2</sub> is the value of capacitor 20. The maximum gain is limited both by the open-loop gain, and by the parasitic floating-gate-to-drain overlap capacitance.

The complementary tunneling and hot-electron injection

The complementary tunneling and not-electron injection processes adjust the floating-gate charge in such a way that the amplifier's output voltage returns to a steady-state value on a slow time scale (on the order of a second or longer) when the injection current is equal to the tunneling current. If the output voltage is below its equilibrium value, then the injection current exceeds the tunneling current, decreasing the charge on the floating gate; that, in turn, increases the output voltage back toward its equilibrium value. If the output voltage is above its equilibrium value, then the tunneling current exceeds the injection current, increasing the charge on the floating gate; that, in turn, decreases the output voltage back toward its equilibrium value. The circuit behaves like a high-pass filter with a long (≥1 second) time constant. The time constant may be set to be arbitrarily long (e.g., minutes, hours, days, etc.)

A Qualitative Presentation of AFGA Operation

Two conditions must be satisfied for the circuit to be in equilibrium. First, the pFET channel current, I<sub>p</sub>, must be equal to the nFET channel current I<sub>n</sub>. The quiescent channel current is defined as  $I_{s0}$ . Second, the injection gate current must be equal to the tunneling current. The quiescent injection current is defined as  $I_{inj0}$  which must equal  $I_{tun0}$ , the quiescent tunneling current, at equilibrium. Since the tunneling and injection currents are many orders of magnitude smaller than  $I_{s0}$  and are charging similarly-sized capacitances, the first condition is satisfied much faster than 35 is the second condition. The frequency range over which the first condition is satisfied, but the second condition is not satisfied, is where the AFGA behaves as an amplifier. The combination of electron tunneling and pFET hot-electron injection applies the appropriate negative feedback to stabilize the output voltage such that the second condition is also satisfied.

In the frequency range where the first condition does not hold, the output voltage is attenuated. In this regime, the circuit behaves as a low-pass filter. Since the output capacitances are charged or discharged by currents on the scale of I<sub>s0</sub> the cutoff frequency will be directly dependent on the bias current. Continuous-time integrators operate on a similar principle, Y. Tsividis, M. Banu, and J. Khaury, "Continuous-time MOSFET-C filters in VLSI", IEEE Transactions on Circuits and Systems, Vol. 33, No. 2, 1986 and C. Mead, Analog VLSI and Neural Systems, Addison-Wesley, 1989. The AFGA transfer function is bandpass, with the low-frequency cutoff set by the equilibrium tunneling and injection currents, and the high-pass cutoff independently set by the equilibrium pFET and nFET channel currents.

FIG. 2 shows the response of the AFGA to a 1 Hz sinewave superimposed on a 19 s input voltage pulse. The AFGA has a closed-loop gain of 11.2, and a low-frequency cutoff at 100 mHz.

If the input changes on a timescale that is much faster than the adaptation, then the output is an amplified version of the input signal. The amplifier adapts to the pulse input after an initial transient, while preserving the amplified 1 Hz sine wave.

The AFGA devices discussed herein were fabricated in the 2-micron n-well Orbit CMOS process available through MOSIS. Typical operating values for  $V_{tun}$  were between

33V and 42V; those for  $V_{dd}$  were between 6V and 12V. Similar data have been obtained with the 1.2-micron n-well Orbit CMOS process, but with typical operating values for  $V_{nun}$  between 26V and 31V. For more modern processes, the typical operating voltages will decrease, because of thinner gate oxides and higher dopant impurity concentrations. Those of ordinary skill in the art will realize that any number of commercially available process technologies may also be used.

Circuit Model of a pFET With Hot-Electron Injection and 10 Electron Tunneling

Before considering the behavior of the autozeroing amplifier, we first review electron tunneling and pFET hot-electron injection. We begin with the basic subthreshold MOS characteristics, C. Mead, Analog VLSI and Neural Systems, Addison-Wesley, 1989, which are valid even at large drain-to-source voltages. For subthreshold operation, the change in the nFET channel current for a change in gate voltage,  $\Delta V_g$ , around a bias current,  $I_{so}$ , can be described as:

$$I_n = I_{so} \exp \left( \frac{\kappa_n \Delta V_g}{U_T} \right) \eqno(EQ. 1)$$

where  $\kappa_n$  is the fractional change in the nFET surface potential due to a change in  $\Delta V_g$ , and  $U_T$  is the thermal voltage, kT/q. The channel current of a pFET is described by:

$$I_p = I_{so} \exp \left( \frac{-\kappa \Delta V_g}{U_T} \right)$$

(EQ. 2) 30

where  $\kappa$  is the fractional change in the pFET surface potential due to a change in  $\Delta V_g$ . Following the conventional definitions of small-signal transconductance,  $g_m$ , and output resistance,  $r_o$ , P. Gray and R. Meyer, *Analysis and Design of Analog Integrated Circuits*, Wiley Interscience, 1984, one obtains the following transconductance and output resistance relationships for a subthreshold pFET:

$$g_m = \frac{\kappa I_{sO}}{U_T}, \text{ and } r_o = \frac{V_o}{I_{sO}} \tag{EQ. 3}$$

FIG. 3 shows how the Early voltage, V<sub>o</sub>, changes when 45 the FETs (both nFETs and pFETs) operate with large drainto-source voltages. The Early voltage is directly related to the amplifier's open-loop gain; for this amplifier, the maximum open-loop gain is roughly 200. The Early voltage decreases at large drain-to-source voltages due to impact 50 ionization in the drain-to-channel depletion region and holes are accelerated to large energies; if a hole has an energy larger than the bandgap, then it may undergo impactionization. The result of an impact ionization is two holes and one electron. For the nFET biased with a drain-to-source voltage of 3.0V and the pFET biased with a drain-to-source voltage of 8.5V, V<sub>o</sub> is nearly constant for both transistors; therefore the AFGA's open-loop gain also is nearly constant.

FIGS. 4A and 4B depict a small-signal model of a pFET with the effects of hot-electron injection. Here a constant tunneling current at the floating gate  $(V_{fg})$  is assumed; this tunneling current sets the bias point for the hot-electron injection parameters.

#### A. Electron Tunneling

Increasing the tunneling voltage, V<sub>tun</sub>, increases the effective electric field across the oxide, which increases the probability of the electron tunneling through the barrier.

8

Typical values for the oxide field range from 0.75V/nm to 1.0V/nm. The classic model of electron tunneling through a silicon/silicon-dioxide system, M. Lenzlinger and E. H. Snow (1969), "Fowler-Nordheim tunneling into thermally grown SiO<sub>2</sub>," *J. Appl. Phys.*, vol. 40, pp. 278–283, 1969, models the electron tunneling current by:

$$I_{tun} = I_o \exp\left(\frac{E_o}{E_{ox}}\right) = I_o \exp\left(\frac{I_{ox}E_o}{V_{tun} - V_{fg}}\right)$$

(EQ. 4)

where  $E_{ox}$  is the oxide electric field,  $t_{ox}$  is the oxide thickness, and  $E_o$  is a device parameter that is roughly equal to 25.6V/nm, is the starting point of the analysis. C. Mead, "Scaling of MOS Technology to Submicrometer Feature Sizes", Journal of VLSI Signal Processing, 8, pp. 9–25, 1994. As showed in P. Hasler, C. Diorio, B. A. Minch and C. Mead, "Single Transistor Learning Synapses", Advances in Neural Information Processing Systems 7, MIT Press, pp. 817–824, 1995. The tunneling current for a fixed bias on the tunneling line is approximated by:

$$I_{nm} = I_{tun0} e^{\frac{\Delta V_{nm} - \Delta V_{fg}}{V_X}}$$

(EQ. 5)

where  $V_x$  is a parameter related to the quiescent tunneling and floating-gate voltages,  $\Delta V_{tun}$  is the change in the tunneling voltage, and  $\Delta V_{fg}$  is the change in the floating-gate voltage from the quiescent floating-gate voltage. For the operating conditions discussed herein, a typical value of  $V_x$  is 1V with the 42 nm oxide used in the 2-micron n-well Orbit process from MOSIS.

#### B. Hot Electron Injection

FIG. **5**A is a band diagram of a subthreshold pFET transistor operating under bias conditions that are favorable for hot-electron injection. Hot-hole impact ionization creates electrons at the drain edge of the drain-to-channel depletion region, due to the high electric fields there. These electrons travel back into the channel region, gaining energy as they go. When their kinetic energy exceeds that of the silicon/silicon-dioxide barrier, they can be injected into the oxide and transported to the floating gate. The hole impactionization current is proportional to the pFET source current, and is the exponential of a smooth function  $(f_1)$  of the drain-to-channel potential  $(\Phi_{dc})$ . This relationship may be expressed:

$$\mathbf{I}_{impaci} = \mathbf{I}_{p} e^{\mathbf{f}_{1}(\Phi_{dc})} \tag{EQ. 6}$$

where  $\Phi_{de}$  is the potential drop from channel to drain. The injection current is proportional to the hole impactionization current, and is the exponential of another smooth function  $(f_2)$  of the voltage drop from channel to drain. This relationship may be expressed:

$$\mathbf{I}_{inj} = \mathbf{I}_{impaci} \mathbf{e}^{f_2(\Phi_{dc})}$$

(EQ. 7)

Because the injection current is only a weak function of the floating-gate voltage for a fixed source current  $(\mathbf{I}_p)$  and  $\Phi_{dc}$ , the gate-voltage dependence may be neglected for this application.

FIG. 5B shows measured pFET injection efficiency for several source currents ( $I_g$ =200 nA, 49 nA, 9 nA, 5 nA). Injection efficiency is the ratio of the injection current to source current. The injection efficiencies are nearly identical for the different source currents; therefore, they appear to be indistinguishable on the plot of FIG. 5B.

The functions  $f_1$  and  $f_2$  are approximately linear over a 1 to 2V change in  $\Phi_{dc}$ . With this linear approximation, the hot-electron injection current may be expressed:

$$I_{inj} = I_{inj0} \frac{I_p}{I_{s0}} \exp\left(\frac{-\Delta \Phi_{dc}}{V_{inj}}\right)$$

(EQ. 8) 5

where  $\Delta\Phi_{dc}$  is the change in  $\Phi_{dc}$  from the quiescent level, and  $V_{inj}$  is a measurable device parameter. For a quiescent  $\Phi_{dc}$ =8.2V, a typical value for  $V_{inj}$  is 250 mV. A decreasing input signal will decrease the pFET surface potential via capacitive coupling to the floating gate. Decreasing the pFET surface potential will increase the source current, thereby decreasing  $\Phi_{dc}$  for a fixed output voltage, and lowering the injection efficiency. Consequently as derived in P. Hasler, C. Diorio, B. A. Minch, and C. Mead, "Single Transistor Learning Synapses", Advances in Neural Information Processing Systems 7, MIT Press, pp. 817–824, 1995, the injection current may be modelled as the  $\alpha$  power of the source current as follows:

$$I_{inj} = I_{inj0} \left(\frac{I_p}{I_{s0}}\right)^{\alpha} \exp\left(\frac{-\Delta V_d}{V_{inj}}\right)$$

$$= I_{inj0} \exp\left(-\frac{\alpha \kappa \Delta V_{fg}}{U_T} - \frac{\Delta V_d}{V_{ini}}\right)$$

(EQ. 9)

where  $I_{so}$  is the quiescent source current,  $V_d$  is the drain  $^{30}$  voltage, and  $\alpha$  is  $1-U_{T}/V_{inj}$ . A typical value of  $\alpha$  is 0.90, which is consistent with  $V_{inj}$  equal to 250 mV.

The small-signal quantifies  $g_{fg}$  and  $r_{fg}$  which are both shown in FIG. 4B can now be expressed, using EQ. 5 and EQ. 9. The term  $g_{fg}$  is defined as the change in the gate current in response to a change in drain voltage. Because only the injection current depends upon the drain voltage,  $g_{fg} = I_{tumo}/V_{inj}$ . The term  $r_{fg}$  is defined for a pFET as the negative change in gate current for a change in gate voltage. Because the effects of both the tunneling and the hotelectron injection processes need to be included, the model for  $r_{fg}$  is

$$\frac{U_T \, / \, \kappa || - V_x}{I_{tunO}} \, ,$$

where x||y=xy/x+y.

Equilibrium Voltages of the AFGA

Qualitatively, two factors change the steady-state output voltage. For the injection current to match the tunneling current after a change in  $V_{\tau}$  or  $V_{uun}$ , the output voltage must reach a new equilibrium. Increasing the bias voltage or channel current requires an increase in the output voltage, 55 because the pFET must reduce its injection efficiency so that the injection current matches the original tunneling current. Increasing the tunneling voltage, which increases the steady-state tunneling current, requires a decrease in the output voltage, because the pFET must increase its injection efficiency so that the injection current matches the new tunneling current.

Above, two conditions for equilibrium were postulated; they are now described quantitatively. Assuming an initial operating point, and considering changes in the steady-state output voltage in response to a change in  $V_{\tau}$  or in  $V_{tun}$ , the current in the nFET must be equal to the current in the pFET:

$$\begin{split} I_n &= I_p \\ I_{so} &\exp \left( \frac{\kappa_n \Delta V_{\tau}}{U_T} \right) = I_{so} \exp \left( \frac{-\kappa \Delta V_{fg}}{U_T} \right) \end{split} \tag{EQ. 10}$$

where  $\Delta V_{\tau}$  is the change in the bias voltage, and  $\Delta V_{fg}$  is the change in the pFET's floating-gate voltage. Therefore, the following relation is obtained:

$$\Delta V_{f_e} = -K_n / K \Delta V_{\tau}$$

(EQ. 11)

Qualitatively, the bias current in the nFET sets the current in the pFET, and therefore sets the floating-gate voltage.

Second, the tunneling current must be equal to the injection current:

$$I_{inj0} {\rm exp} \bigg( \frac{-\alpha \kappa \Delta V_{fg}}{U_T} \bigg) {\rm exp} \bigg( \frac{-\Delta V_{out}}{V_{inj}} \bigg) = I_{nun0} {\rm exp} \bigg( \frac{\Delta V_{nun} - \Delta V_{fg}}{V_x} \bigg) \eqno(EQ.~12)$$

Here, if it is assumed that  $I_{inj0}$  is equal to  $I_{nm0}$  at the initial operating point, the second equilibrium relationship is obtained:

$$\Delta V_{out} = -\frac{V_{inj}}{V_x} \Delta V_{tun} + V_{inj} \frac{\kappa_n}{\kappa} \left( \frac{\alpha \kappa}{U_T} - \frac{1}{V_x} \right) \Delta V_{\tau}$$

(EQ. 13)

For above-threshold operation, the above equation becomes

$$\Delta V_{out} = -\frac{V_{inj}}{V_x} \Delta V_{tun} + V_{inj} \frac{\kappa_n}{\kappa} \left( \frac{2}{V_{dd} - V_{fg} + V_T} - \frac{1}{V_x} \right) \Delta V_\tau \tag{EQ. 14}$$

FIGS. 6A–6B show the measured change in the steady-state output voltage versus circuit parameters. Both data sets agree with the model described in EQ. 13. The AC gain of this amplifier was 146. FIG. 6A shows the steady-state output voltage versus the tunneling voltage for three values of  $V_{\tau}$ . FIG. 6B shows the steady-state output voltage versus  $V_{\tau}$  for two tunneling voltages (36.35V, 36.9V). The curves begin to saturate for above-threshold bias currents, as predicted by EQ. 14.

An ideal amplifier is insensitive to variations in the bias voltages; the data in FIGS. 6A-6B show the circuit's DC sensitivity to  $V_{\tau}$  and  $V_{tun}$ . First, the DC gain from the tunneling node to the output is given by  $V_{inj}/V_{x}$ , which, for the measured data shown, is 0.64. The DC gain from the nFET gate to the output is given by

$$V_{inj}\frac{\kappa_n}{\kappa}\bigg(\frac{\alpha\kappa}{U_T}-\frac{1}{V_x}\bigg),$$

which, for the measured data shown, is 10. The DC gain from the input to the output is zero. All three gains are smaller than the AFGA AC gain of 146.

Under the proper bias conditions, the power-supply rejection depends on the choice of reference. With the input and output referred to  $V_{dd}$ , and with  $V_{\tau}$  referred to GND, the AFGA gain from the power-supply to the output is 0.1, which results in a passband power-supply rejection ratio of 64 dB. The power-supply rejection ratio is limited by the open-loop gain of the amplifier. If instead all nodes are referred to GND, the AC power supply gain is 146, which decreases the passband power-supply rejection ratio to 0 dB. The circuit designer must also be careful of where the floating-gate capacitances are connected; for good power

supply rejection, all these capacitors must be referenced to  $V_{dd}$ . Otherwise, the power supply becomes another input to the AFGA and any AC power supply noise will appear at the output, amplified by the AFGA's AC gain.

The steady-state output voltage and the high-pass cut-off frequency are set explicitly by  $V_{nm}$  and by the power-supply voltage. Increasing  $V_{nm}$  increases the tunneling current, which in turn decreases the settling time, but it also decreases the steady-state output voltage, since the pFET must have a larger drain-to-source voltage. Increasing the power-supply voltage decreases the tunneling current by decreasing the voltage across the oxide, increasing the settling time and increasing the steady-state output voltage. Low Frequency AFGA Behavior

Two general equations can be written which govern the autozeroing floating-gate amplifier behavior around an equilibrium output voltage. The first equation is obtained by applying Kirchoff's current law (KCL) at the floating gate:

$$(C_1 + C_2 + C_w) \frac{dV_{fg}}{dt} =$$

$$(EQ. 15)$$

$$C_1 \frac{dV_{in}}{dt} + C_2 \frac{dV_{out}}{dt} + I_{tuno} \left( 1 - \exp\left(-\alpha \kappa \Delta \frac{V_{fg}}{U_T} - \frac{\Delta V_{out}}{V_{ini}}\right) \right)$$

The second equation is obtained by applying KCL at the 25 output node:

$$(C_2 + C_L)\frac{dV_{out}}{dI} = C_2\frac{dV_{fg}}{dI} + I_v\left(\exp\left(-\frac{\kappa\Delta V}{U_T}\right) - 1\right)$$

(EQ. 16)

This neglects the Early effect, which adds a correction term to EQ. 16. As long as the closed-loop gain is much lower than the amplifier gain, ignoring the Early effect is a good approximation.

In the passband, where the AFGA is an amplifier, the floating gate is held nearly fixed by the amplifier feedback, and the tunneling and injection currents are negligible. This approximation simplifies EQ. 15 to

$$C_2 \frac{dV_{out}}{dt} = -C_1 \frac{dV_{in}}{dt}$$

(EQ. 17)

thus, the change in the output voltage ( $\Delta V_{out}$ ) is equal to the input voltage ( $\Delta V_{in}$ ) amplified by  $-C_1/C_2$ .

A. Low-Frequency Model

Two approximations are made here to model the low frequency response of the AFGA. First, the open-loop gain from the floating gate to the output can be large; a typical value is 700. To keep the output voltage between the supply rails, the floating gate voltage is confined to a 10 mV swing. Thus, the floating-gate voltage is approximated by a constant value. Second, because the floating-gate voltage is nearly constant, the source current varies only slightly. The quiescent source current ( $I_{s0}$ ) is set by the nFET current source. From EQ. 5 and EQ. 9, the model of injection current for a fixed source current  $I_{s0}$  is therefore:

$$I_{tun} - I_{inj} = I_{tun0} \left( 1 - \exp\left(-\frac{\Delta V_{out}}{V_{ini}}\right) \right)$$

(EQ. 18)

where  $I_{nun0}=I_{inj0}$  for the circuit in equilibrium. Since the floating gate is held nearly constant by feedback, the floating-gate voltage dependence in EQ. 9 is negligible. 65 Even when the circuit is biased with above-threshold currents, the tunneling current still is nearly fixed. Since the

12

injection efficiency is still an exponential function of the drain voltage for above-threshold currents, the lowfrequency dynamics are similar in below- and abovethreshold operation.

With the above approximations, the amplifier's output voltage,  $V_{out}$ , can be modeled in terms of  $V_{in}$ , with a single equation. The total floating-gate current is the sum of the capacitive currents of the input and output terminals, plus the tunneling and injection currents. From EQ. 15:

$$C_2 \frac{d V_{out}}{d t} = -C_1 \frac{d V_{in}}{d t} + I_{tuno} \left( \exp \left( -\frac{\Delta V_{out}}{V_{ini}} \right) - 1 \right)$$

(EQ. 19)

To solve EQ. 19, make the following change of variables:

$$X = e^{\frac{\Delta V_{cout}}{V_{inj}}}$$

(EQ. 20)

The resulting equation for X is a linear, first-order differential equation with variable coefficients

$$\tau_{l}\frac{dX}{dt} = -\frac{\tau_{l}A_{v}X}{V_{lnj}}\frac{dV_{ln}}{dt} + 1 - X \tag{EQ. 21} \label{eq:equation:equation:equation}$$

where  $\tau_1$ , the low-frequency cutoff, is equal to  $C_2 V_{inj}/I_{tum0}$ , and  $A_\nu$  is the closed-loop AC gain of the amplifier,  $-C_1/C_2$ .

#### B. Response to a Voltage Step

Consider the AFGA's response to an input voltage step. Assume that the output voltage has adapted initially to its steady-state value. To solve EQ. 21, first assume that the output voltage immediately after applying the step,  $\Delta V_{out}$  (0<sup>+</sup>), is given by the magnitude of the input step times the AFGA AC gain. Employing  $\Delta V_{out}$  (0<sup>+</sup>) as a new, effective initial condition, and denoting the effective initial condition in X by:

$$X(0^+) = \exp\left(\frac{V_{out}(0^+)}{V_{inj}}\right)$$

(EQ. 22)

For a downward step,  $X(0^+)$  is greater than 1; for an upward step,  $X(0^+)$  is less than 1. After the input step,  $dV_{in}/dt=0$ ; therefore EQ. 21 becomes:

$$\tau_1 \frac{dX}{dt} = 1 - X$$

(EQ. 23)

$X(0) = X(0^+)$

The solution to EQ. 23 in terms of  $\Delta V_{out}$  is

$$\Delta V_{out}(t) = V_{inj} \ln \left( 1 + (X(0^+) - 1) \exp\left(\frac{-t}{\tau_t}\right) \right)$$

(EQ. 24)

where  $\Delta V_{out} \rightarrow 0$  as  $t \rightarrow \infty$ .

The step response has three interesting regimes, which are approximated by

The first case occurs when the tunneling current is nearly equal to the injection current just after the voltage step. The solution in this region is the familiar exponential decay of a linear system. The second case occurs when the tunneling current dominates the injection current. The behavior of the output voltage in this regime results from the constant 15 tunneling current removing electrons from the floating gate. The third case occurs when the injection current dominates the tunneling current.

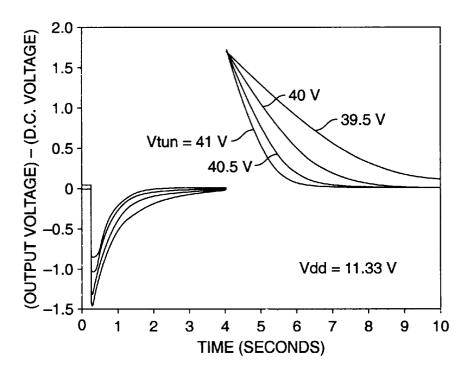

FIGS. 7A-7B shows the response of the AFGA to an upgoing and downgoing step input. The adaptation in response to an upward step results from electron tunneling; the adaptation in response to a downward step results from pFET hot-electron injection. This amplifier had a gain of 11.2. FIG. 7A shows a plot of the curve fits of the simplified expressions of EQ. 25, where either tunneling or injection dominates the restoration process. From the fits,  $\tau_1$  is 4.3 s and  $I_{tun0}$  is 50 fA. The value of  $\tau_1$  can be set reliably to more than  $10^5$  seconds. FIG. 7B shows the response to a square wave for four different values (41V, 40.5V, 40V, 39.5V) of the tunneling voltage. This amplifier of FIG. 7B had a gain of 147; the input square wave is not shown. The steady-state output voltage decreased in the same manner as seen in FIG. 6B for increasing tunneling voltages. The initial tail in the upgoing response is due to the output voltage going to ground. FIG. 7A shows a measured response to an input pulse, with curve fits to the regions here either the tunneling or injection current dominates.

#### C. Long-Term Parameter Drift

The physical properties of the tunneling and hot-electron 40 injection mechanisms change with time. These processes are permanently modified as electrons pass through the oxide, creating electron traps. The long-term changes were investigated by performing an accelerated stress experiment, where an AFGA was continuously operated for 145 hours 45 with an average  $\tau_1$  of 1.7 s. When used as an amplifier or as a low-pass filter, a more reasonable  $\tau_1$  would be at least several minutes; therefore, this experiment is equivalent to the stress of operating the AFGA continuously for a few years. The effect of an input signal only slightly modifies the 50 results of this experiment. To characterize the behavior of the AFGA over time, a similar square wave experiment to the one shown in FIGS. 7A-7B was performed once per hour for 145 hours. To each of the resulting output waveforms, the expressions of EQ. 25 were fit and the  $_{55}$  feedthrough. Defining  $\tau_h$ : relevant device parameters were extracted.

FIGS. 8A and 8B show the effect of operating an AFGA for a long time. In FIG. 8A the response to an upgoing and downgoing voltage step before and after 145 hours of operation is shown. The difference in the output voltage from its equilibrium DC level is plotted as a function of time; the equilibrium output voltage slightly increased from the 145 hours of operation. In FIG. 8B the extracted device parameters as a function of time are shown. Since I<sub>nun0</sub>/C<sub>2</sub> changes more than V<sub>inj</sub>, one can see that most of the long term change is due to the tunneling junction, which is probably due to oxide trapping.

14

High-Frequency AFGA Behavior

For sufficiently high frequencies, the AFGA is a low-pass filter. In this regime, the tunneling and injection currents are negligible; therefore EQ. 15 is approximated by:

$$(C_1 + C_2 + C_w) \frac{dV_{fg}}{dt} = C_1 \frac{dV_{in}}{dt} + C_2 \frac{dV_{out}}{dt}$$

(EQ. 26)

From EQ. 26, changes in  $V_{out}$  are proportional to changes in  $V_{fg}$  and  $V_{in}$ . At extremely high frequencies, the transistor channel currents are negligible compared to the capacitive currents. In this capacitive-feedthrough regime, the solutions to EQ. 16 and EQ. 26 are

$$\frac{\Delta V_{fg}}{\Delta V_{in}} = \frac{C_1(C_2 + C_L)}{(C_1 + C_2 + C_w)(C_2 + C_L) - C_2^2}$$

$$\frac{\Delta V_{out}}{\Delta V_{in}} = \frac{C_1 C_2}{(C_1 + C_2 + C_w)(C_2 + C_L) - C_2^2}$$

(EQ. 27)

The effects of the capacitive feedthrough can be reduced by increasing either  $C_L$  or  $C_w$ .

At frequencies between the low-frequency cutoff and the capacitive-feedthrough regime, the behavior of the AFGA results from the floating-gate voltage settling back to its equilibrium value. Therefore, combining EQ. 16 and EQ. 26 into a single equation for the floating-gate voltage:

$$((C_1 + C_2 + C_w)(C_2 + C_L) - C_2^2) \frac{dV_{fg}}{dI} =$$

$$(EQ. 28)$$

$$(C_1 + C_2 + C_w)(C_2 + C_L) - C_2^2) \frac{dV_{fg}}{dI} + C_2 I_{\tau} \left( e^{-\frac{\kappa \Delta V_{fg}}{U_T}} - 1 \right)$$

This equation is similar to EQ. 21, which describes the output-voltage response in the low-frequency case. Substituting:

$$Y = e^{\frac{\kappa \Delta V_{fg}}{U_T}}$$

(EQ. 29)

into EQ. 28 results in the linear differential equation:

$$\tau_h \frac{dY}{dt} = \frac{\tau_{h2} \kappa}{U_T} \frac{dV_{in}}{dt} Y + 1 - Y \tag{EQ. 30}$$

where  $\tau_{h2}$  is defined to be:

$$\tau_{h2} = \frac{C_1(C_2 + C_L)U_T}{\kappa C_2 I_\tau} \tag{EQ. 31} \label{eq:theta2}$$

which is the time constant that marks the onset of capacitive

$$\tau_h = \frac{((C_1 + C_2 + C_w)(C_2 + C_L) - C_2^2)U_T}{\kappa C_2 I_\tau} \tag{EQ. 32}$$

which represents the high-frequency cutoff.

As in the low-frequency case, the response to an input voltage step will be considered. To solve EQ. 30, first assume that the floating-gate voltage immediately after applying the step,  $\Delta V_{fg}(0^+)$ , is given by the magnitude of the input step attenuated by the capacitive divider ratio, EQ. 27. With this initial condition, the solution is:

$$\Delta V_{fg} = \frac{U_T}{u} \ln \left( 1 + \left( e^{\frac{\kappa \Delta V_{fg}^{(0^+)}}{U_T}} - 1 \right) e^{-\frac{t}{\tau_{fh}}} \right)$$

(EQ. 33)

After the initial jump, given by EQ. 27, the output voltage is related to the floating-gate voltage by:

$$\Delta V_{out} = \frac{C_1 + C_2 + C_w}{C_2} \Delta V_{fg}$$

(EQ. 34)

FIGS. 9A-9B show the high-frequency AFGA behavior. In FIG. 9A, voltage vs. time curves for two AFGAs with unity gain are shown, but with each having different values for C<sub>1</sub>. The larger-capacitor circuit had C<sub>1</sub>=C<sub>2</sub>=300fF, whereas the smaller-capacitor circuit had  $C_1 = C_2 = 50 fF$ . For both AFGAs, C<sub>L</sub> was the same. The two AFGAs are operating the different subthreshold bias currents in order to achieve comparable settling times. As in the low-frequency case, the high-frequency response of the AFGA is asymetric: the downgoing step response approaches its steady state linearly with time, and the upgoing step response approaches its steady state logarithmically with time. The initial jump in the downgoing step is due to capacitive feedthrough. From these data, it is evident that decreasing  $C_1$  and  $C_2$  without changing  $C_L$  will decrease the amount of capacitive feedthrough. FIG. **9**B shows the voltage responses to a small input step for two AFGAs with respective gains of 1 and 146. The response from the unity-gain 30 AFGA (at the bottom) shows a linear, first-order, low-pass filtered version of the input. These responses illustrate the gain-bandwidth tradeoff in the AFGA.

The linear 3V output swing in the high-gain response of FIG. 9B raises the question: What determines the linear range of an AFGA? The criterion for linearity is that  $\Delta V_{fg}$  be sufficiently small that the factor,

$$\bigg( \exp \! \bigg( \! - \frac{\kappa \Delta V_{f\!g}}{U_T} \bigg) \! - 1 \bigg),$$

in EQ. 28 can be approximated by  $-\kappa\Delta V_{fg}/U_T$ . This criterion implies that the floating-gate voltage must not move by more than  $U_{T}/\kappa$  from its equilibrium value. The floating-gate 45 voltage has its maximum swing in the capacitive-feedthrough regime; therefore, from EQ. 27 the input linear range,  $V_{Li}$ , is

$$V_{Li} = \frac{U_T}{\kappa} \left( \frac{C_1 + C_2 + C_w}{C_1} \right) B$$

(EQ. 35)

where:

$$B = 1 - \frac{C_2^2}{(C_1 + C_2 + C_w)(C_I + C_2)}$$

(EQ. 36)

For amplifiers with gains greater than or equal to one, which requires that  $C_1$  be greater than  $C_2$ , B is bounded between ½ and 1 for all  $C_1$ ,  $C_2$ ,  $C_w$ , and  $C_L$ . Further, if the AFGA is driving a  $C_L$  that is at least as big as  $C_1$ , B is bounded between ¾ and 1. Consequently, B can be considered a correction term.

The output linear range,  $V_{Lo}$ , is expressed in terms of the input linear range,  $V_{Li}$ , by:

$$V_{Lo} = \frac{U_T}{\kappa} \left( \frac{C_1 + C_2 + C_w}{C_2} \right) B$$

(EQ. 37)

which is  $V_{Li}$  times the amplifier gain,  $C_1/C_2$ . The output linear range scales with the amplifier gain. By increasing  $C_{\nu\nu}$ , the change in the floating-gate voltage can be reduced, thereby increasing the amplifier's output linear range. The AFGA's gain from input to output in the passband is:

$$\frac{V_{out}}{V_{in}} = -\frac{C_1}{C_2} \frac{1}{1 + \frac{C_1 + C_2 + C_w}{C_2 A}} = -\frac{C_1}{C_2} \frac{1}{1 + \frac{\kappa V_{Lo}}{A U_T B}}$$

(EQ. 38)

where A is the gain from floating gate to output. For a sufficiently large A, the AFGA's passband gain is independent of C.

FIGS. 10A–B show the linear range of the AFGA versus  $C_w$ . In FIG. 10A the response of three AFGAs to the same square wave input is shown. Here all three AFGAs were the same except for their values of  $C_w$  and were biased by the same  $V_r$ . Increasing  $C_w$  increases the linear range, decreases the amount of capacitive feedthrough, and decreases the low-pass cutoff frequency. FIG. 10B shows the measured linear range and  $\tau_h$  for several unity-gain AFGAs for different  $C_w$  ratioed in units of  $C_1$ . Both curves in FIG. 10B are fitted with a linear equation. For a unity gain AFGA, that is  $C_1$ = $C_2$ , the expressions for  $\tau_h$  and input linear range are:

$$\tau_h = \frac{U_T(C_1 + C_L)}{\kappa I_{\tau}} \left( 2 - \frac{C_1}{C_1 + C_L} + \frac{C_w}{C_1} \right)$$

(EQ. 39)

and:

$$V_{Li} = \frac{U_T}{\kappa} \left( 2 - \frac{C_1}{C_1 + C_L} + \frac{C_w}{C_1} \right)$$

(EQ. 40)

The data in FIGS. 10A–B was taken with AFGAs that had no explicitly drawn  $C_L$ ; the variation between the data and the linear curve fit is most likely due to the different parasitic load capacitances. Both from experimental data and the direct analytic solution of EQ. 30, second harmonic distortion dominates for the AFGAs; for a sine-wave input with amplitude of  $V_{Li}$ , the peak second harmonic distortion is 0.05 percent of, or 26 dB below, the fundamental frequency response. The second harmonic distortion is maximum for frequencies just below  $1/2 \pi t_h$ ; for amplitudes at or below  $V_L$ , the second harmonic distortion is proportional to the square of the fundamental amplitude.

(EQ. 35) 50 Frequency Response of the AFGA

In order to derive the AFGA frequency response, one begins with the small-signal form of EQ. 15 and EQ. 16:

$$(C_1 + C_2 + C_w) \frac{dV_{fg}}{dt} = C_1 \frac{dV_{in}}{dt} + C_2 \frac{dV_{out}}{dt} + \frac{I_{tun0}}{V_{inj}} \Delta V_{out},$$

(EQ. 41)

$$(C_2 + C_L) \frac{dV_{out}}{dt} = C_2 \frac{dV_{fg}}{dt} - \frac{\kappa I_{\tau}}{U_T} \Delta V_{fg}$$

that is, one assumes that the input signal is sufficiently small that one needs to keep only the linear terms when expanding the exponentials. A small-signal input changes  $V_{out}$  by less than  $V_{inj}$ , due to the injection nonlinearity in the low-frequency regime, and  $V_{fg}$  by less than  $U_T/\kappa$ , due to the transistor nonlinearity in the high-frequency regime.

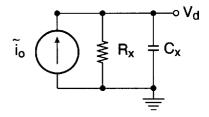

FIGS. 11A-C depict an AFGA represented as a smallsignal circuit. FIG. 11A shows the small-signal AFGA model

17

using the small-signal pFET model. FIG. 11B shows the small-signal model of the effect of the noise source in the channel on the output voltage. The effect of the gate current and the Early voltage effect has been neglected here. FIG. 11C shows a simplified small-signal model of the effect of noise. For clarity, we define

$$R_x = \frac{C_1 + C_2 + C_w}{g_m C_2}, \text{ and}$$

$$C_x = C_L + C_2 \left(1 - \frac{C_2}{C_1 + C_2 + C_w}\right).$$

EQ. 41 can also be obtained by analyzing the small-signal circuit in FIG. 11A. The response in the low-frequency and high-frequency regimes, which typically do not interact will be discussed in turn. Finally, the general solution will be presented.

For low-frequency inputs, one can approximate EQ. 41 as:

$$\tau_{t} \frac{C_{1}}{C_{2}} \frac{dV_{in}}{dt} + \tau_{t} \frac{dV_{out}}{dt} = -\Delta V_{out}$$

(EQ. 42)

for which the resulting frequency response is:

$$\frac{V_{out}(s)}{V_{in}(s)} = -\frac{C_1}{C_2} \frac{s\tau_1}{1 + s\tau_1}$$

(EQ. 43)

For high-frequency inputs, one can simplify EQ. 41 by assuming input frequencies much larger than  $1/2 \pi \tau_1$ , which are written:

$$\frac{V_{out}}{V_{in}} = -\frac{C_1}{C_2} \frac{1 - \tau_{h2}s}{1 + \tau_{hS}}$$

(EQ. 44)

This transfer function includes the effects of parasitic and load capacitances. The response in EQ. 44 is the transfer function of a first-order system; because capacitive feedback is used, the AFGA is stable for any value of closed loop gain. As seen in FIG. 12,  $\tau_h$  is 265  $\mu$ sec for the high-gain AFGA, and  $\tau_h$  is 4  $\mu$ sec for the low-gain AFGA.

The response for all frequencies is obtained by taking the Laplace transform of EQ. 41, which is

$$\begin{split} s(C_1+C_2+C_w)V_{fg} &= sC_1V_{in} + \left(sC_2 + \frac{I_{nno}}{V_{inj}}\right)V_{out},\\ s(C_2+C_L)V_{out}(s) &= \left(sC_2 + \frac{\kappa I\tau}{U_T}\right)V_{fg} \end{split} \tag{EQ. 45}$$

EQ. 45 is solved to obtain:

$$\frac{V_{out}(s)}{V_{in}(s)} = -\frac{C_1}{C_2} \frac{1 - \tau_{h2}s}{1 + \tau_{h}s + \frac{1}{\tau_{co}}}$$

(EQ. 46) 55

where  $\tau_1$ ,  $\tau_h$ ,  $\tau_{h2}$  were defined previously.

FIG. 12 shows the frequency response for two AFGAs with different gains. The high-gain AFGA has a gain of 146, and the low-gain AFGA has unity gain. For both the high and low-gain AFGA,  $C_1+C_2$  is approximately constant. For the high-gain AFGA,  $\tau_1$  is 8 sec, and  $\tau_h$  is 265  $\mu$ sec; for the low-gain AFGA,  $\tau_1$  is 530 sec and  $\tau_h$  is 4  $\mu$ sec. The ratio of  $\tau_h$  and  $\tau_1$  between the two AFGAs are equal to half of the ratio of the gains, which is consistent with a constant  $C_1+C_2$ .

18

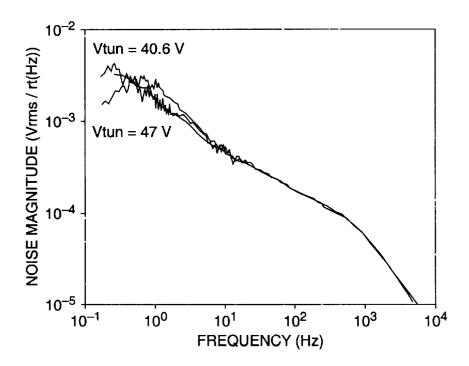

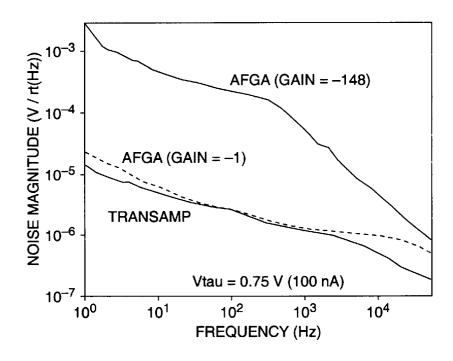

When considering the frequency response of the AFGA, it is natural to consider the output-voltage spectrum for no input—that is, the output voltage noise from the amplifier. FIGS. 13A–13B show AFGA output-voltage spectrums for a fixed voltage-source input. For low frequencies, 1/f noise is dominant, and for high frequencies, thermal noise dominates. The AFGA filters the 1/f noise below the low-frequency cutoff.

FIGS. 13A-B depict a noise spectrum of an AFGA for a constant input. FIG. 13A shows the output noise spectrum of an AFGA with a gain of 146 for two different tunneling voltages  $(V_{tun})$ . The high-frequency cutoff eliminates 1/fnoise at frequencies below  $1/\tau_I$ , The spectrum was taken for a bias current of 80 nA, which corresponds to V, of 0.73 V. FIG. 13B shows a comparison of a high-gain AFGA with a unity gain AFGA and a generic follower-connected differential amplifier. All three amplifiers had the same V, voltage, and correspondingly had the same bias current. The sum of C<sub>1</sub> and C<sub>2</sub> is the same for both AFGAs. FIG. 13A shows that we can reduce the 1/f noise by increasing  $V_{nun}$ , and thereby decreasing  $\tau_1$ . FIG. 13B shows a comparison between a high-gain AFGA, a unity gain AFGA, and a followerconnected transconductance amplifier. The transconductance amplifier is the wide-range amplifier as described in C. Mead, Analog VLSI and Neural Systems, Addison-Wesley, 1989; it has larger transistors than do the AFGAs, resulting in the lower 1/f noise in FIG. 13B. The AFGAs used a constant tunneling current; therefore, we conclude that the tunneling and injection processes do not significantly contribute to the noise levels.

It is of interest to investigate how changing the AFGA design will change the amount of output noise. Following Rahul Sarpeshkar, Tobias Delbruck, and Carver A. Mead, "White Noise in MOS Transistors and Resistors," IEEE Circuits and Devices, November 1993, pp. 23–29., one can model the thermal noise component,  $\hat{1}_o$  of a subthreshold MOSFET's channel current by:

$$\frac{\hat{l}_o^2}{\Delta f} = \frac{2}{\kappa} q U_T g_m r \tag{EQ. 47}$$

Because the AFGA's output comprises both an nFET and a pFET, the total thermal-noise current derives from two parallel noise sources. To find the output-referred voltage noise, the simplified small-signal circuit of FIG. 11B can be used. The small-signal circuit of FIG. 11B can be further simplified to that shown in FIG. 11C, by noting that one can relate  $V_{fg}$  to  $V_{out}$  by a capacitive divider. From this simpler circuit, we express the signal power of the output-referred voltage noise,  $\hat{V}^2_{out}$  can be expressed as:

$$\hat{V}_{out}^{2} = \left(\frac{C_{1} + C_{2} + C_{w}}{C_{2}g_{m}}\right)^{2} \frac{\hat{i}_{o}^{2}}{1 + (\omega \tau_{h})^{2}}$$

(EQ. 48)

where  $\tau_h$  was defined above. From this expression, the total-output-noise power is:

$$\hat{V}_{out}^2 = \frac{4}{\kappa} q U_T g_m \left( \frac{C_1 + C_2 + C_w}{C_2 g_m} \right)^2 \int_0^\infty \frac{1}{1 + (\omega \tau_b)^2} df$$

which, using EQ. 32 evaluates to:

$$\hat{V}_{out}^2 = \frac{qU_T}{\kappa B} \frac{C_1 + C_2 + C_w}{C_2(C_L + C_2)}$$

(EQ. 49)

with the correction term, B, as defined in EQ. 36. The total-output-noise power is roughly proportional to  $C_w$  and inversely proportional to  $C_L$ . R. Sarpeshkar, R. F. Lyon, and C. Mead, "A low-power wide-linear-range transconductance amplifier", Analog Integrated Circuits and Signal Processing, in Press. See also, U.S. Pat. No. 5,463,348 entitled "CMOS Low-Power, Wide-Linear-Range, Well-Input Differential and Transconductance Amplifiers".

To calculate the dynamic range of an AFGA one may define the dynamic range (DR) in terms of signal power as the ratio of the maximum possible output swing corresponding to the input linear range and an input that has an equivalent swing to the total-output-noise power. With this definition, which is equivalent to EQ. 12, we can express the dynamic range for the AFGA as:

$$DR = \frac{V_{Lo}^2}{2\hat{v}^2} = \frac{\kappa}{2q} V_{Lo} (C_L + C_2) B^2$$

(EQ. 50)

which is a similar form for dynamic range for the wide-linear-input-range amplifier discussed in R. Sarpeshkar, R. F. Lyon, and C. Mead, "A low-power wide-linear-range transconductance amplifier", Analog Integrated Circuits 30 and Signal Processing, in Press. See also U.S. Pat. No. 5,463,348 entitled "CMOS Low-Power, Wide-Linear-Range, Well-Input Differential and Transconductance Amplifiers". Like the wide-linear-input-range amplifier, this amplifier increases dynamic range by amplifying the signal more than 35 the total amplifier noise. The cost for this performance enhancement is a proportional increase in the power dissipation. Another direct result of this expression is that the dynamic range varies inversely with C2; therefore, a highgain amplifier will have a larger dynamic range than the 40 low-gain amplifier for the same C1, Cw, and CL. Steady-State Output-Voltage Dependence On The Output

In this section, the dependence of the steady-state output voltage on the amplitude of the input signal is discussed. 45 Consider the range of frequencies in which the input voltage changes at a rate that is much slower than the circuit's integrating behavior, but is much faster than the adaptation due to the tunneling and injection currents; that is, the input is entirely in the AFGA's passband.

Signal

FIG. 14 shows measurements of the minimum and maximum output voltages versus output amplitude. For small input amplitudes, the minimum and maximum output symmetrically diverge from the steady-state voltage, but for large input amplitudes, most of the change in the output  $_{55}$  voltage is due to the maximum of the output voltage increasing. In general, the steady-state output voltage converges to within about  $V_{ini}$  of the minimum of the signal.

To analyze this effect, we decompose the output voltage into components that change at fast and slow rates. We assume that we can express the output voltage as a sum of fast and slow variables; that is:

$$\Delta V_{out} = \Delta \hat{V}_{out} + \Delta \hat{V}_{out}$$

(EQ. 51)

where  $\Delta \hat{V}_{out}$  represents the fast-timescale behavior, and is 65 the amplified version of  $\Delta V_{in}(\Delta \hat{V}_{out} = -C_1/C_2\Delta V_{in})$ , and  $\Delta$   $\overline{V}_{out}$  represents the slow-timescale behavior. With this

**20**

formulation, EQ. 51 can be integrated over a large number of periods of the fast timescale, but can still make only a small change in the slow-timescale output voltage. E[.] shall mean the average of a time-varying signal, x(t), over a time interval, T, that is sufficiently shorter than the slow timescale, but is much longer than the shortest period of the fast variables:

$$E[x(t)] = \frac{1}{T} \int_{0}^{T} x(t)dt$$

(EQ. 52)

By this definition,

$$E\left[\frac{dV_{in}}{dt}\right] \to 0, E\left[\frac{dV_{out}}{dt}\right] \to \frac{dV_{out}}{dt}$$

(EQ. 53)

The resulting equation in  $\Delta \overline{V}_{out}$  is

$$C_{2} \frac{d \overline{V}_{out}}{d t} = I_{tuno} \left( E \left[ e^{-\frac{\Delta V_{out}}{V_{inj}}} \right] - 1 \right)$$

(EQ. 54)

25 Expressing

$$E\left[e^{-\frac{\Delta V_{out}}{V_{inj}}}\right]$$

in terms of the fast and slow variables:

$$E\left[e^{-\frac{\Delta V_{Out}}{V_{inj}}}\right] = e^{-\frac{\Delta V_{Out}}{V_{inj}}}Q$$

(EQ. 55)

$$Q = E \left[ e^{-\frac{\Delta V_{OM}}{V_{inj}}} \right]$$

(EQ. 56)

Rewriting EQ. 54 as:

$$C_2 \frac{d\overline{V}_{out}}{dt} = I_{tun0} \left( Q e^{-\frac{\Delta \overline{V}_{out}}{V_{inj}}} - 1 \right)$$

(EQ. 57)

From the analysis above, the solution to EQ. 54 is:

$$\Delta \overline{V}_{out} = V_{inj} \ln \left( Q + \left( e^{-\frac{V_{out}(0+)}{V_{inj}}} - Q \right) e^{-\frac{t}{\tau}} \right)$$

(EQ. 58)

where the steady state solution for  $\Delta \overline{V}_{out}$  is:

$$\Delta \overline{V}_{out} = V_{inj} \ln \left( E \left[ e^{-\frac{\Delta \overline{V}_{out}}{V_{inj}}} \right] \right)$$

(EQ. 59)

The amplifier always adapts such that the minimum of the output signal always returns to the equilibrium output voltage.

Now, consider the behavior of the output voltage as a function of different amplitude sine waves applied to the input. The version of the input signal after it is amplified by the AFGA is defined as  $\Delta\hat{V}_{out}$ =A sin ( $\omega t$ ); for this output signal, the steady state voltage is:

21 22

$$\Delta \overline{V}_{out} \approx V_{inj} \ln \left( \frac{2}{3} + \frac{1}{3} \cosh \left( \frac{A}{2V_{inj}} \right) \right)$$

(EQ. 60)

FIG. 14 shows, for an AFGA with a gain of 146, the measured minimum and maximum output voltages verses peak-to-peak output-voltage amplitude. The frequency of the input sine wave was 100 Hz. For small input amplitudes, the minimum and maximum output voltages symmetrically diverge from the steady state voltage, but for large input amplitudes, most of the output voltage change follows the maximum output voltage. The DC voltage was fit to the function 0.25 ln (0.667+0.333exp( $V_{dc}/0.62$ )), which is nearly equal to EQ. 60.

## Other AFGA Effects

#### A. Modeling the Above-Threshold AFGA

The operation of an autozeroing floating-gate amplifier operating with above threshold bias currents does not change from the subthreshold case in three important respects. First, those effects that depend on electron tunneling remain the same, because tunneling is not a function of the MOSFET channel current. Second, the injection current is still the exponential of roughly the same function of the drain voltage. Third, the low frequency dynamics should remain unchanged for a constant C<sub>2</sub>, because the channel 25 current is still nearly fixed by feedback.

The pFET hot-electron injection model changes for above-threshold bias currents in two ways. First, the source current is not an exponential function of the gate voltage, but varies quadratically with the gate voltage. Second, although 30 operating the AFGA above threshold has little effect on the hot-electron-injection efficiency, the injection current/source current efficiency will decrease above threshold because the impact-ionization efficiency will decrease, because the channel potential decreases near the drain edge with decreasing 35 gate voltage. The above-threshold injection-current model from EQ. 9 can be modified to be:

$$\begin{split} I_{inj} &= I_{inj0} \bigg( \frac{V_{dd} - V_{fg} - \Delta V_{fg} + V_T}{V_{dd} - V_{fg} + V_T} \bigg)^2 e^{-\frac{\Delta V_{d} - \kappa \Delta V_g}{V_{inj}}} \\ &\approx I_{inj0} \bigg( 1 - \frac{2\Delta V_{fg}}{V_{dd} - V_{fg} + V_T} \bigg) e^{-\frac{\Delta V_{d} - \kappa \Delta V_g}{V_{inj}}} \\ &\approx I_{inj0} \exp \bigg( -\frac{2\Delta V_{fg}}{V_{dd} - V_{fg} + V_T} \bigg) e^{-\frac{\Delta V_d}{V_{inj}}} \end{split}$$

This model modifies the DC output voltage, as mentioned above, to be:

$$\Delta V_{out} = -\frac{V_{inj}}{V_x} \Delta V_{tun} + V_{inj} \frac{\kappa_n}{\kappa} \left( \frac{2}{V_{dd} - V_{fg} + V_T} - \frac{1}{V_x} \right) \Delta V_{\tau} \tag{EQ. 62} \label{eq:equation:equation:equation}$$

Recall from FIG. 6, that the equilibrium output voltage versus the bias current began to saturate for above-threshold bias currents.

Now consider how the high frequency behavior changes for above-threshold bias currents. For above-threshold currents, EQ. 28 is modified to:

$$\tau_h \frac{d\,V_{fg}}{d\,t} = \tau_{h2} \frac{d\,V_{in}}{d\,t} - \Delta V_{fg} \left( 1 - \frac{\kappa \Delta V_{fg}}{V_{dd} - \kappa (V_{fg0} + V_{70})} \right) \eqno(EQ.\,63)$$

The definitions of  $\tau_h$  and  $\tau_{h2}$  are similar to their subthreshold definitions,

$$\tau_{h2} = \frac{C_1(C_2 + C_L)(V_{dd} - \kappa(V_{fg0} + V_{T0}))}{\kappa C_2 I_{\tau}}$$

(EQ. 64)

and

$$\tau_h = ((C_1 + C_2 + C_w)(C_2 + C_L) - C_2^2) V_{dd} - \frac{\kappa (V_{fg0} + V_{70})}{\kappa C_2 I_{\tau}} \tag{EQ. 65} \label{eq:eq. 65}$$

The higher bias current results in a higher cutoff frequency, but also requires an increase in power dissipation. The linear input range of the amplifier is larger than it is for subthreshold bias currents. The linear input voltage range is

$$\frac{C_1+C_2+C_w}{\kappa C_1}(V_{dd}-\kappa(V_{fgO}+V_{TO})).$$

The large-signal dynamics change for above threshold biases, when the input voltage exceeds its linear range. The floating-gate-to-drain capacitance is a function of the drain voltage, which adds additional dynamics to the large signal response.

FIG. 15 shows the response of an above threshold autozero amplifier to a slow downgoing step. The capacitance of the floating-gate changes with the output voltage due to the change in the capacitance between the output and the floating gate.

B. Continuous Operation of the Tunneling Current

It is of interest to understand what happens when a continuously operating tunneling current is not present in the AFGA. The constant tunneling bias current naturally eliminates the effect of DC biasing points; without this current, the circuit is no longer an autozeroing amplifier. Without the constant tunneling current, circuitry must be added to remove the effect of the DC input voltage. Furthermore, additional 1/f noise is generated in this floating-gate amplifier, since the high-pass behavior, due to the floating-gate adaptation, filters out a substantial amount of 1/f noise.

Assume that one wants to autozero the floating-gate amplifier only to set a particular operating point. Then, after this calibration phase, one needs to lower the tunneling voltage and power supply to turn off the electron-tunneling and hot-electron-injection processes to eliminate the oxide currents. Unfortunately, the capacitive coupling of the tunneling junction and capacitances not referenced to V<sub>dd</sub> to the floating gate will make potentially large changes in the output voltage. This effect can be minimized by using small tunneling junctions and by ensuring that all the capacitances (including all parasitics) coupling into the floating gate are referenced to V<sub>dd</sub>.

In addition to the capacitive coupling, the charge on the floating gate will change due to electron traps in the oxides. When tunneling or injecting electrons into SiO<sub>2</sub>, a portion of these electrons will become trapped in the oxide, E. H. Nicollian and J. R. Brews, MOS Physics and Technology, Wiley Interscience, 1982. In addition, as more current passes through these oxides, more electron traps are created, C. Hu, S. Tam, F. Hsu, P. Ko, T. Chan, and K. Terrill, "Hot-Electron-Induced MOSFET Degradation-Model, Monitor and Improvement", IEEE Transactions on Electron Devices, Vol. ED-32, No. 2, February 1985, pp. 375–385. After the oxide currents stop, some of these trapped electrons will become free thermally, and will find their way to the floating gate. This effect will result in a large drift in the output voltage over time for the same input bias voltage.

FIG. 16 shows the change in the AFGA output voltage with and without a continuous tunneling current. An AFGA

10

with a gain of 146 was used for each case. The case for no tunneling current also required dropping the power supply;  $V_{dd}$  was set at 5V. The trace with no tunneling current was taken five minutes after the tunneling line was dropped. The change in the output voltage over time for a high-gain AFGA with and without a constant tunneling current is shown in FIG. 16. The detrapping effect in this high-gain AFGA shows no sign of stopping until the output runs into ground; in a lower-gain circuit, the detrapping may eventually settle out within the power supply.

C. Restoration to Equilibrium of an Output Voltage when Starting at the Voltage Rails

What happens when the output voltage starts at one of the supply rails? The output voltage starts at  $V_{dd}$  when the floating-gate voltage is too low. In this regime, there is no 15 injection current, and the tunneling current removes electrons from the floating gate, raising the floating-gate voltage. Eventually, the floating-gate voltage increases to its steadystate level, and the output voltage decreases from  $V_{dd}$ . If the output voltage starts near ground, then the pFET cannot get 20 sufficient channel current to develop enough injection to balance the tunneling current. The current must be balanced by changes in the floating-gate voltage: in this case, the floating-gate voltage will increase, since the tunneling current is stronger than the pFET injection current. Unfortunately, the resulting pFET channel current will decrease even further, and that will decrease the injection current, leading to a runaway condition. The steady-state output voltage may not return to the original equilibrium level. Typically, this condition poses no problem even for reasonably large changes in the input voltage; however, this effect is seen when large changes in  $V_{\tau}$  are made. Decreasing  $V_{tun}$ , decreasing the input voltage, increasing  $V_{\tau}$ , or increasing  $V_{dd}$  might allow the AFGA to recover from this condi-

An Implementation Of An AFGA In Silicon